# Software Overview

# **TABLE OF CONTENTS**

| TABLE OF CONTENTS                                                                                                         | 1        |

|---------------------------------------------------------------------------------------------------------------------------|----------|

| LIST OF TABLES                                                                                                            | 5        |

| LIST OF FIGURES                                                                                                           | <i>6</i> |

| 1 Introduction                                                                                                            | 8        |

| 1.1 Where to Get More Information                                                                                         | 8        |

| 2 Introducing cnMIPS (Cavium Networks MIPS)                                                                               | 9        |

| 3 Introducing the Simple Executive API                                                                                    | 10       |

| 4 Runtime Environment Choices for cnMIPS Cores                                                                            | 13       |

| 4.1 Performance Difference Between Simple Executive and Linux                                                             | 14       |

| 4.2 Simple Executive                                                                                                      |          |

| 4.3 SMP Linux                                                                                                             |          |

| 4.3.1 Linux: <i>embedded_rootfs</i> File System                                                                           | 16       |

| 4.3.2 Linux: Debian File System                                                                                           | 17       |

| 4.3.3 Linux Application Support                                                                                           | 17       |

| 4.3.3 Linux Application Support                                                                                           | 18       |

| 4.3.5 Simple Executive API Calls From Linux                                                                               | 18       |

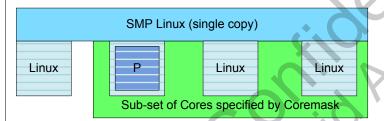

| 4.3.6 CPŪ Affinity                                                                                                        |          |

| 4.3.7 Linux on Small Systems (Limited MBytes of Memory)                                                                   |          |

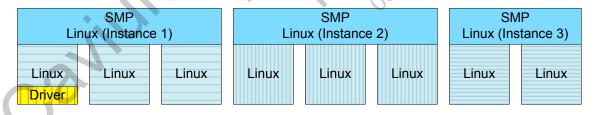

| 4.3.8 Running Multiple Linux Kernels on the OCTEON Processor                                                              |          |

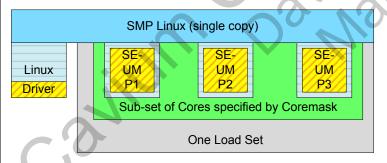

| 4.4 Hybrid Systems: Simple Executive and Linux Co-Existing                                                                | 20       |

| <ul> <li>4.5 System Initialization</li> <li>4.6 The Hardware Simulator</li> <li>4.7 Other Runtime Environments</li> </ul> | 21       |

| 4.6 The Hardware Simulator                                                                                                | 21       |

| 4.7 Other Runtime Environments                                                                                            | 21       |

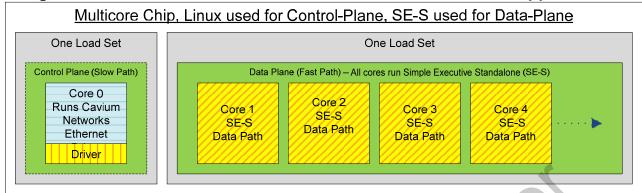

| 5 Combinations of Runtime Environments on One Chip                                                                        |          |

| 5.1 One-Core Runtime Choices                                                                                              |          |

| 5.2 Multicore Runtime Choices                                                                                             |          |

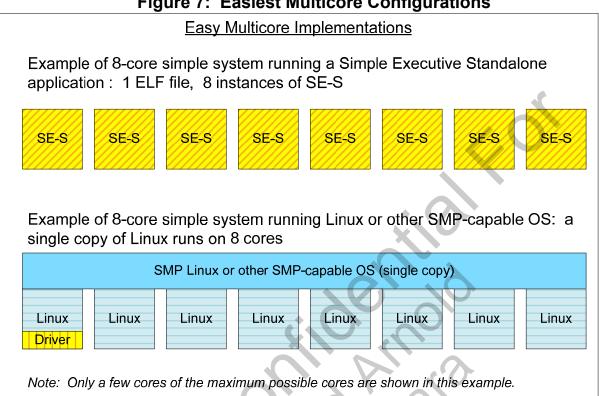

| 5.2.1 Easiest Configurations to Implement                                                                                 |          |

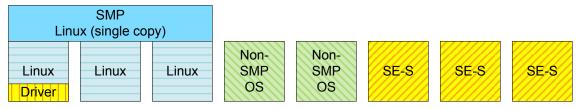

| 5.2.2 Intermediate Configurations                                                                                         | 23       |

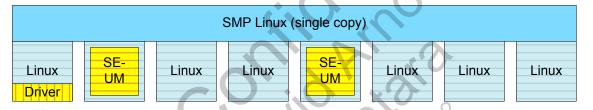

| 5.2.3 Advanced Configurations                                                                                             |          |

| 5.3 Application Entry Point and Startup Code                                                                              |          |

| 5.4 Booting SE-S or SE-UM Applications                                                                                    |          |

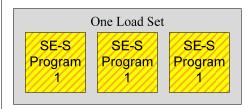

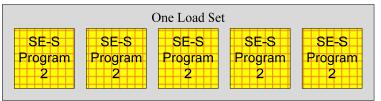

| 5.5 Booting One ELF File on Multiple Cores: Load Sets                                                                     |          |

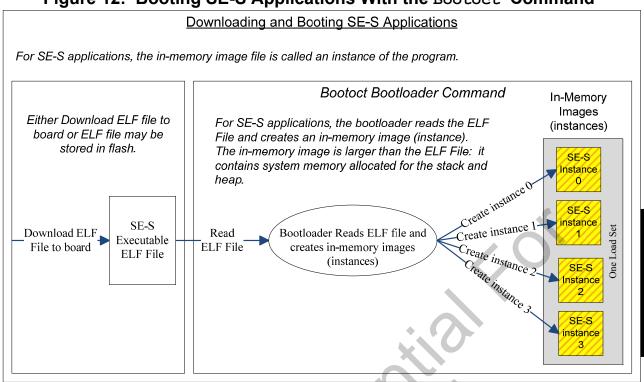

| 5.5.1 Starting SE-S Applications With the bootoct Command                                                                 |          |

| 5.5.2 Starting Linux With the bootoctlinux Command                                                                        |          |

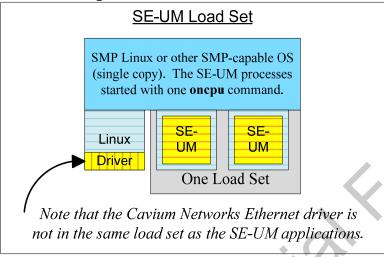

| 5.5.3 Starting SE-UM Applications With the oncpu Command                                                                  | 29       |

| 5.6 Booting Different ELF Files                                                                                           | 32       |

|   | 5.7 Synchronizing Multiple Cores                               | 32 |

|---|----------------------------------------------------------------|----|

|   | 5.7.1 Synchronizing Cores in the Same Load Set                 |    |

|   | 5.7.2 Synchronizing Cores in Different Load Sets               | 33 |

|   | 5.7.3 SMP Linux Synchronization                                |    |

|   | 5.7.4 Multiple SE-S or SE-UM ELF Files (Not Recommended)       | 34 |

| 6 |                                                                |    |

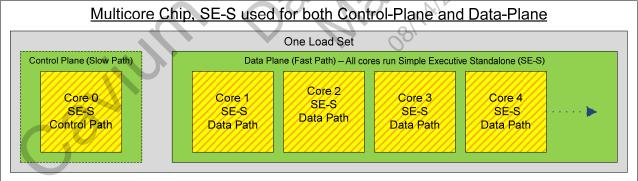

|   | 6.1 Control-Plane Versus Data-Plane Applications               | 36 |

|   | 6.2 Event-driven Loop (Polling) Versus Interrupt-Driven Loop   |    |

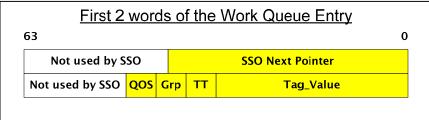

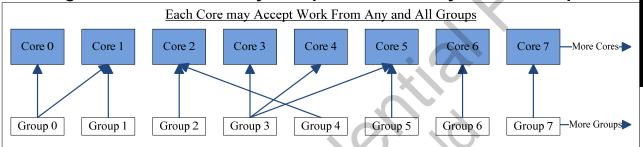

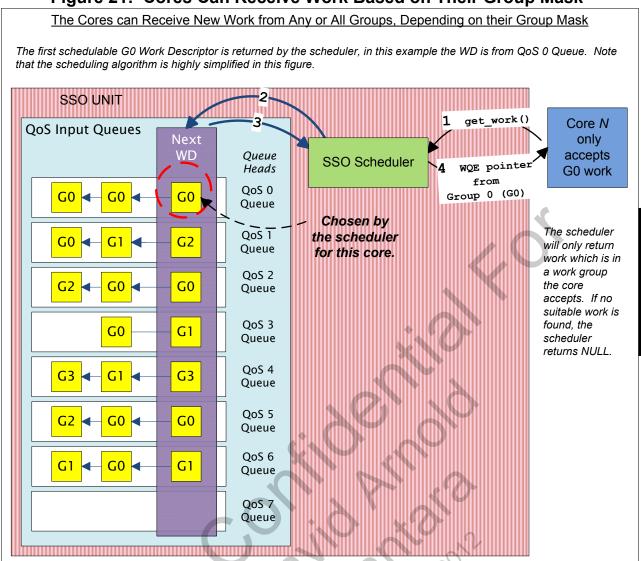

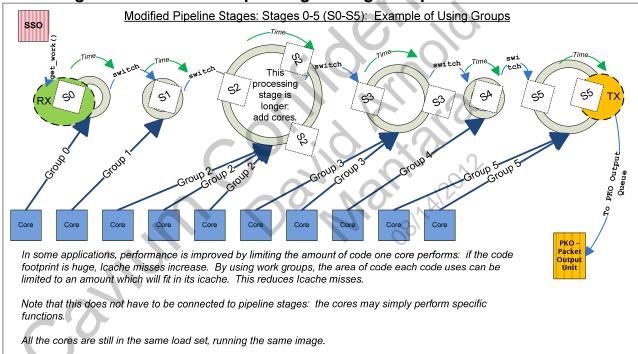

|   | 6.3 Using Work Groups in Packet Processing                     | 38 |

|   | 6.3.1 Work Groups                                              | 38 |

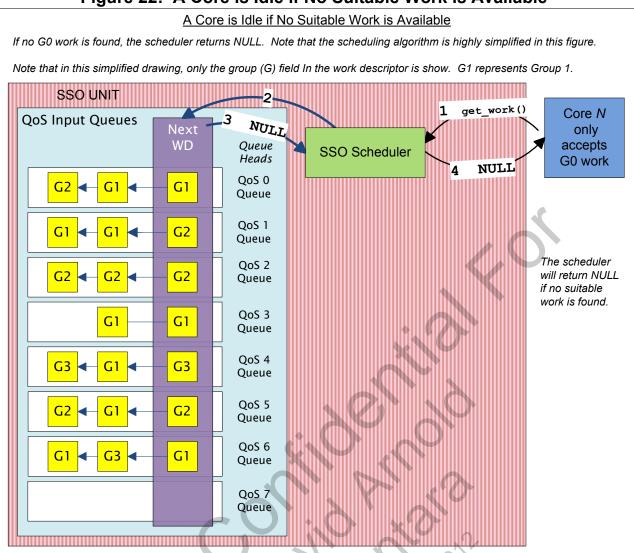

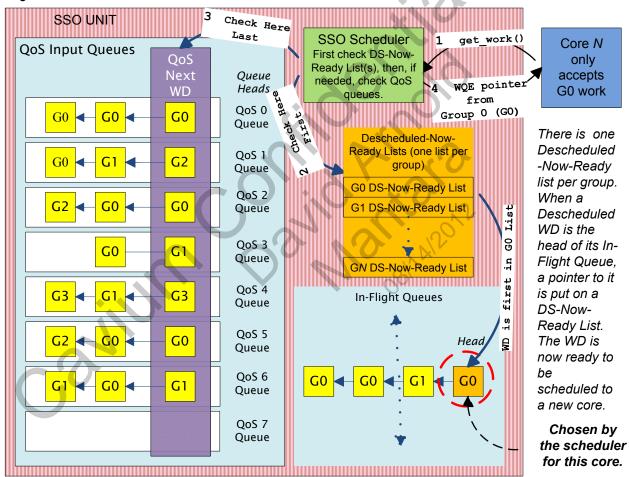

|   | 6.3.2 Configuring the Per-Core Group Mask in the SSO Scheduler | 39 |

|   | 6.4 Pipelined Versus Run-To-Completion Software Architecture   | 45 |

|   | 6.4.1 Comparing Run-To-Completion and Traditional Pipelining   | 45 |

|   | 6.4.2 A Quick Look at Packet Processing Math                   | 46 |

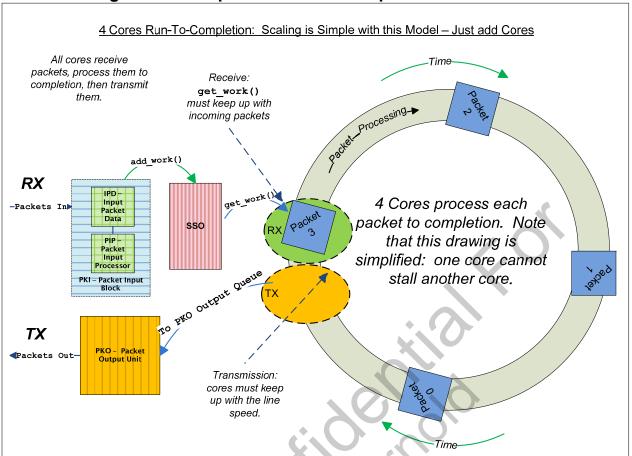

|   | 6.4.3 Run-To-Completion                                        | 49 |

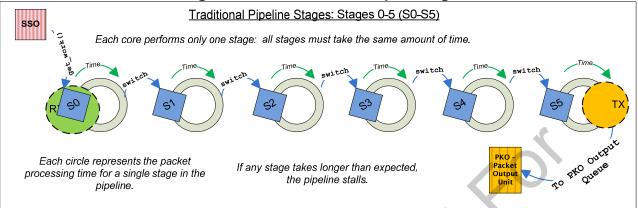

|   | 6.4.4 Traditional Pipelining                                   |    |

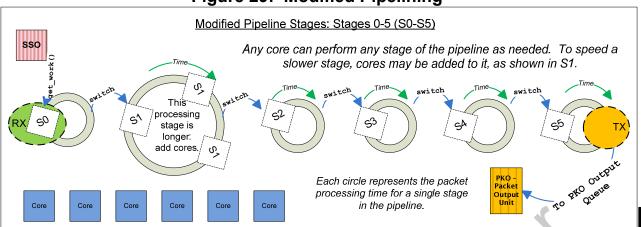

|   | 6.4.5 Modified Pipelining                                      | 52 |

|   | 6.5 Other Software Architecture Issues                         | 54 |

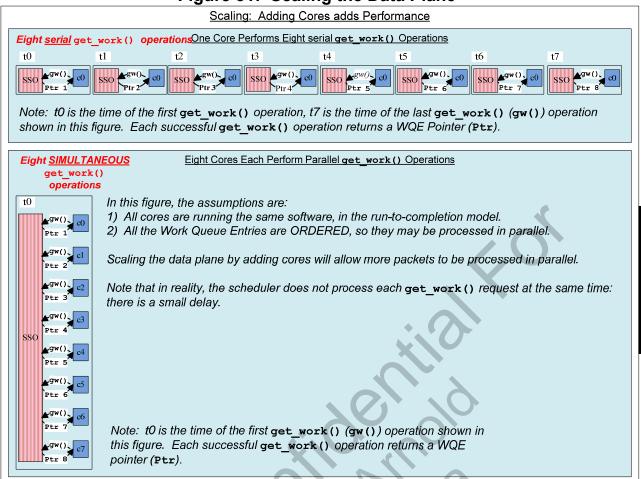

|   | 6.5.1 Scaling                                                  |    |

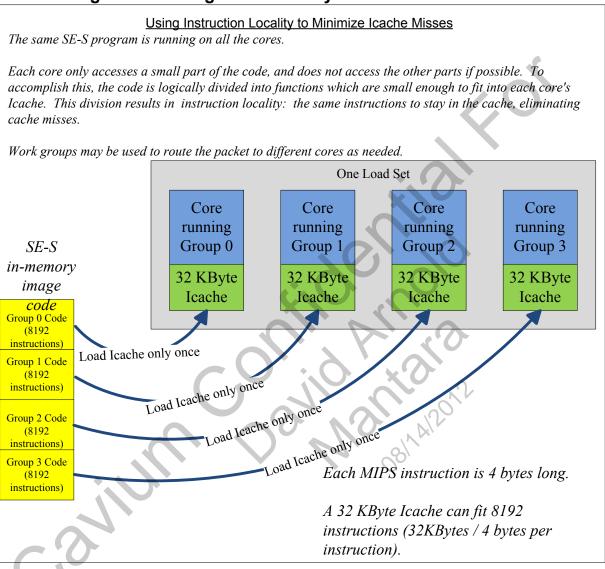

|   | 6.5.2 Code Locality: Reducing Icache Misses                    |    |

|   | 6.5.3 Load-Balancing                                           | 57 |

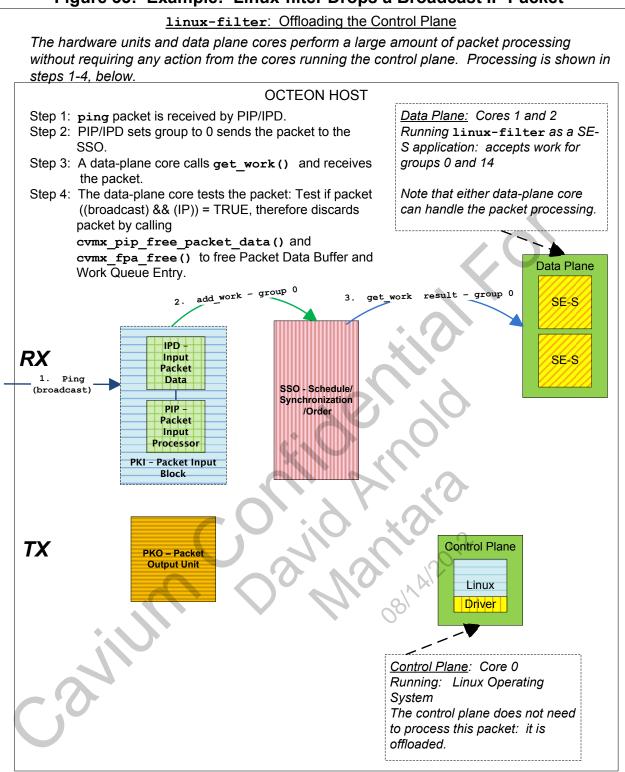

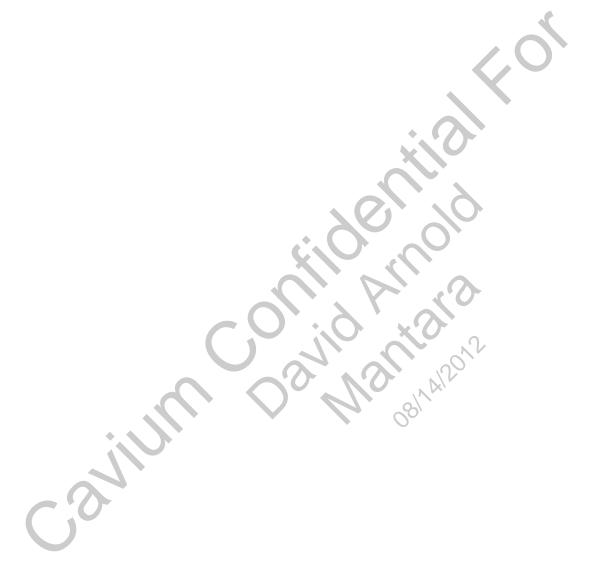

|   | 6.6 Example: linux-filter                                      | 57 |

| 7 |                                                                | 62 |

|   | 7.1 ABI Choices                                                |    |

|   | 7.1.1 EABI (OCTEON_TARGET=cvmx_64): SE-S 64-Bit                |    |

|   | 7.1.2 N64 (OCTEON_TARGET=linux_64): SE-UM 64-Bit               | 62 |

|   | 7.1.3 N32 (OCTEON_TARGET=cvmx_n32): SE-S 32-Bit                | 62 |

|   | 7.1.4 N32 (OCTEON_TARGET=linux_n32): SE-UM 32-Bit              | 63 |

|   | 7.1.5 O32 (linux_o32) (Not Recommended)                        | 63 |

|   | 7.1.6 Linux uclibc (linux_uclibc)                              | 63 |

|   | 7.1.7 Choosing the OCTEON_TARGET                               | 63 |

|   | 7.2 64-Bit Porting Issues                                      | 63 |

| 8 | Tools                                                          | 66 |

|   | Tools                                                          | 66 |

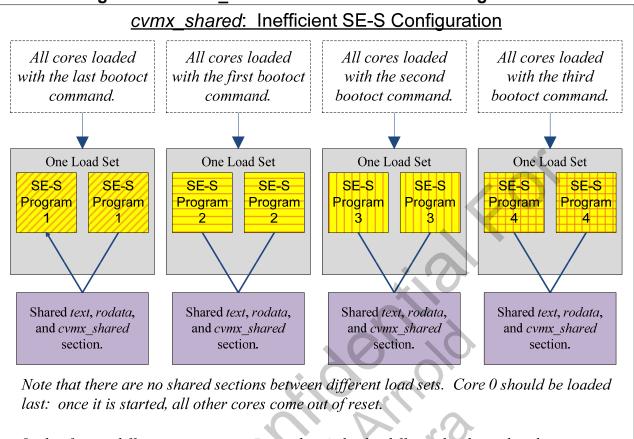

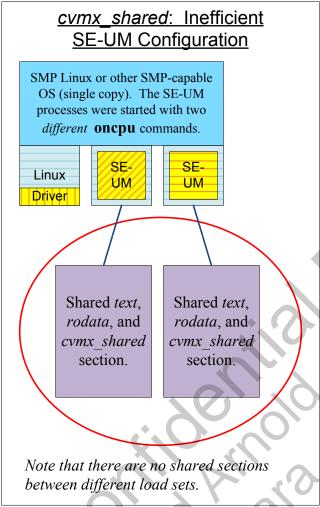

|   | 8.1.1 The Cavium Networks-Specific <i>cvmx_shared</i> Section  | 66 |

|   | 8.1.2 Link Addresses                                           | 68 |

|   | 8.1.3 Simple Executive Development Tools                       |    |

|   | 8.1.4 Linux Development Tools                                  |    |

|   | 8.2 Native Tools (Run on the Target)                           |    |

|   | 8.2.1 Native tools and Simple Executive                        |    |

|   | 8.2.2 Native tools and Linux                                   |    |

| 9 | J                                                              |    |

|   | 9.1 Physical Address Map                                       |    |

|   | 9.2 System Memory (DRAM) Addresses                             |    |

|   | 9.3 I/O Space Addresses                                        |    |

|   | 9.4 Caching                                                    | 74 |

| 9.5    | Special L2 Cache Features: Partitioning and Locking                               | 76  |

|--------|-----------------------------------------------------------------------------------|-----|

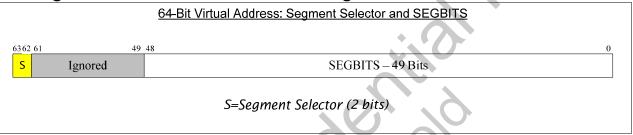

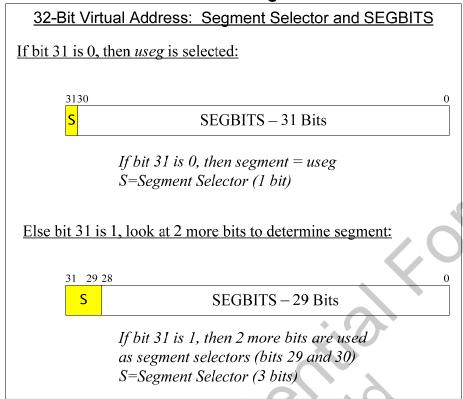

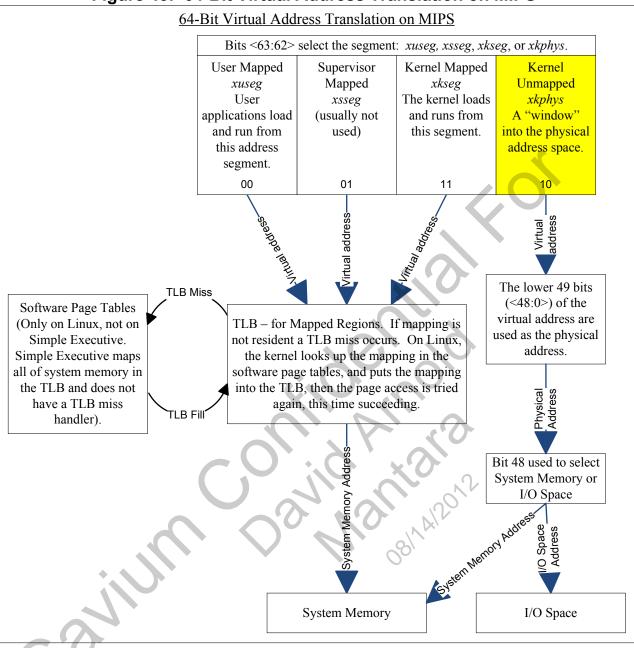

| 10 Vir | tual Memory                                                                       |     |

| 10.1   | Virtual Address Translation                                                       |     |

| 10.    | 1.1 Mapping                                                                       | 77  |

| 10.    | 1.2 The Translation Look-Aside Buffer (TLB)                                       |     |

| 10.    | 1.3 Wired TLB Entries                                                             |     |

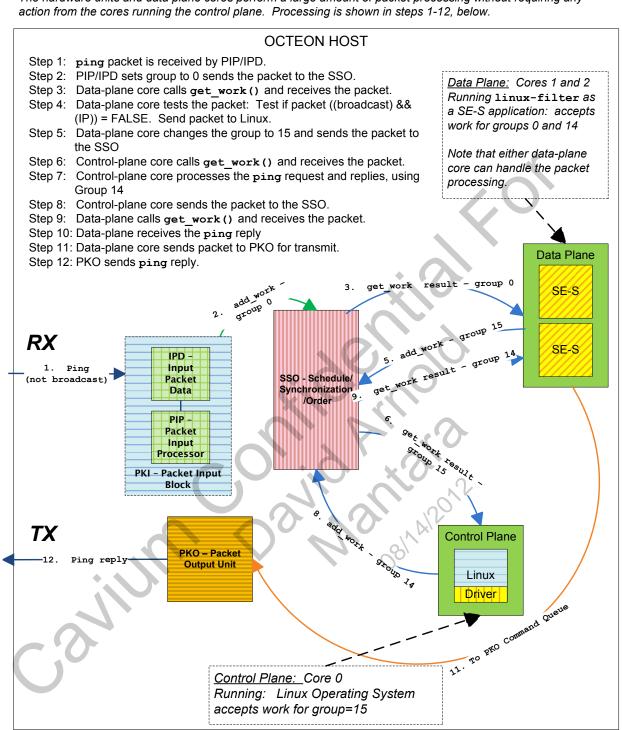

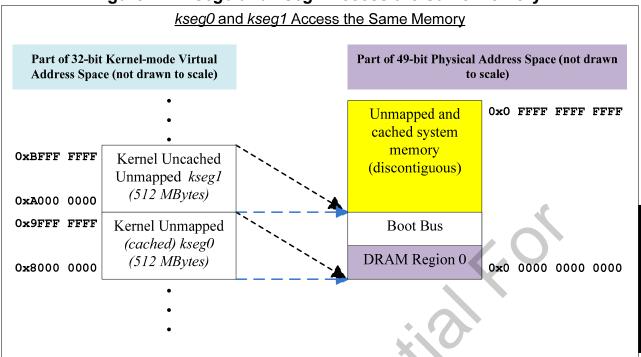

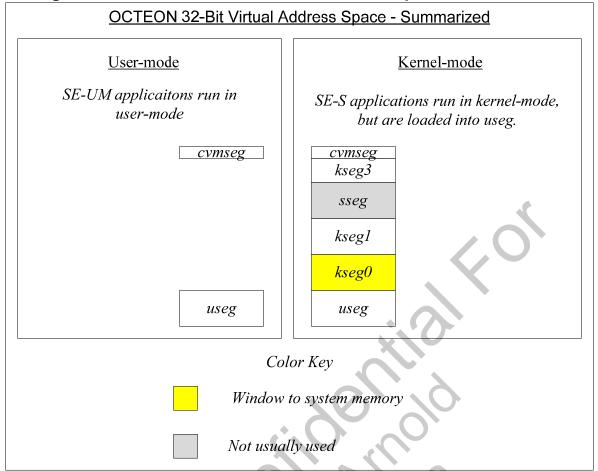

| 10.2   | Generic MIPS Virtual Memory Map                                                   | 78  |

| 10.3   |                                                                                   |     |

| 10     |                                                                                   |     |

| 10     | 3.2 Privilege Level (Mode) and Segments                                           | 81  |

| 10.4   |                                                                                   |     |

| 10.4   |                                                                                   |     |

| 10.4   | 4.2 Mapped Segments                                                               | 85  |

| 10.4   | 4.3 Addresses Versus Pointers                                                     | 87  |

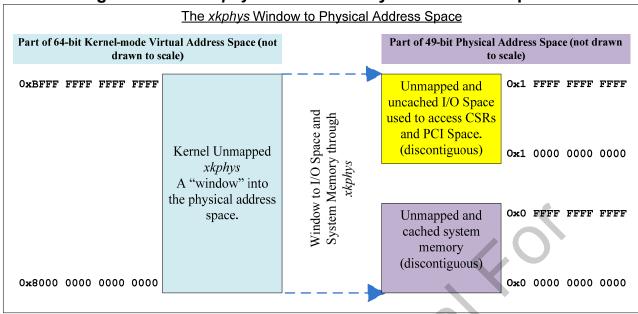

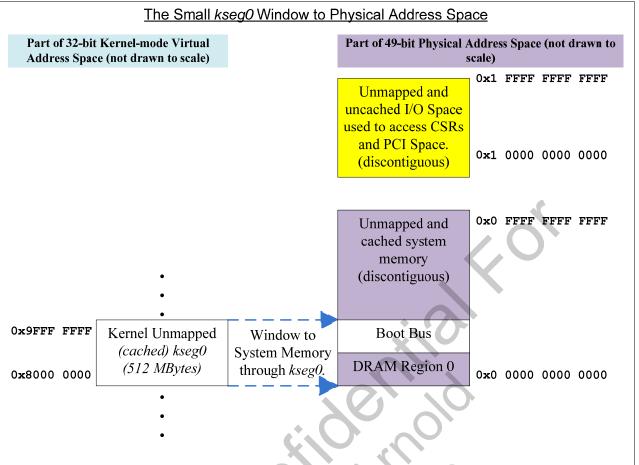

| 10.5   | Virtual Memory onCavium Networks MIPS (cnMIPS)                                    | 88  |

| 10.6   | Cavium Networks-Specific cymseg Segment                                           | 89  |

| 10.7   | Accessing Application-Private System Memory                                       | 90  |

| 10.8   | Summary of Virtual Address Space on cnMIPS                                        | 90  |

| 11 All | Summary of Virtual Address Space on cnMIPSocating and Using Bootmem Global Memory | 94  |

| 11.1   | Using Global Bootmem                                                              | 94  |

| 11.2   | The malloc() and free() Functions and FPA Buffers                                 |     |

| 11.3   | The cvmx_shared Section and FPA Buffers                                           | 97  |

| 11     |                                                                                   |     |

| 11     | 3.2 The <i>cvmx_shared</i> Section Should be Kept Small                           | 99  |

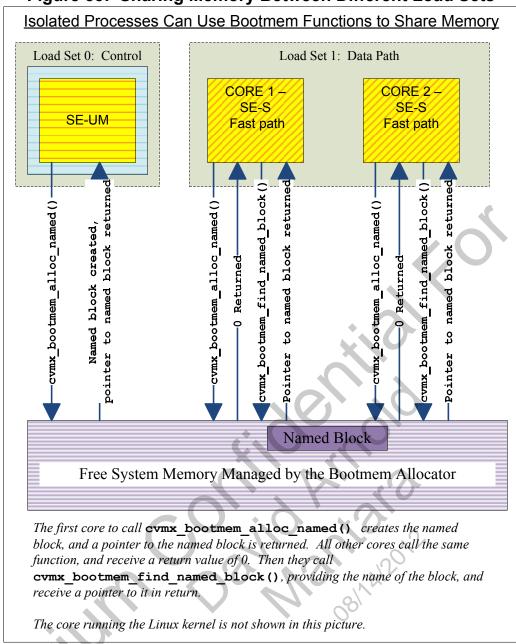

| 11.4   | Using Named Blocks to Share Memory Between Different Load Sets                    | 100 |

| 12 Acc | cessing Bootmem Global Memory (Buffers)                                           | 102 |

| 12.1   | Accessing Bootmem Global Memory From SE-S Applications                            | 104 |

| 12.    |                                                                                   | 104 |

| 12.    | 1.2 SE-S 32-Bit Bootmem Access                                                    |     |

| 12.2   | Accessing Bootmem Global Memory From Linux Kernel: 64-Bit                         |     |

| 12.3   |                                                                                   | 105 |

| 12     |                                                                                   |     |

| 12     | 3.2 SE-UM 32-Bit Bootmem Access  Bootmem Size in Different Access Methods         | 105 |

| 12.4   | Bootmem Size in Different Access Methods                                          | 106 |

| 12.5   | Using cvmx_ptr_to_phys() and cmvx_phys_to_ptr() Functions                         | 107 |

| 13 Acc | cessing I/O Space                                                                 |     |

| 13.1   | Accessing I/O Space from SE-S Applications                                        |     |

| 13.    | 1.1 SE-S 64-Bit I/O Space Access                                                  |     |

|        | 1.2 SE-S 32-Bit I/O Space Access                                                  |     |

| 13.2   | Accessing I/O Space from Linux Kernel: 64-Bit                                     |     |

| 13.3   | Accessing I/O Space from SE-UM Applications                                       |     |

| 13     | 1                                                                                 |     |

|        | 3.2 SE-UM 32-Bit I/O Space Access                                                 |     |

|        | nple Executive Standalone (SE-S) Memory Model                                     |     |

| 14.1   | Simple Executive Application Space                                                |     |

| 14.2   | Simple Executive System Memory Access                                             | 109 |

| 14.2.1 Mapping of System Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 14.3 Simple Executive I/O Space Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 113 |

| 14.4 Simple Executive Virtual Memory Configuration Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 113 |

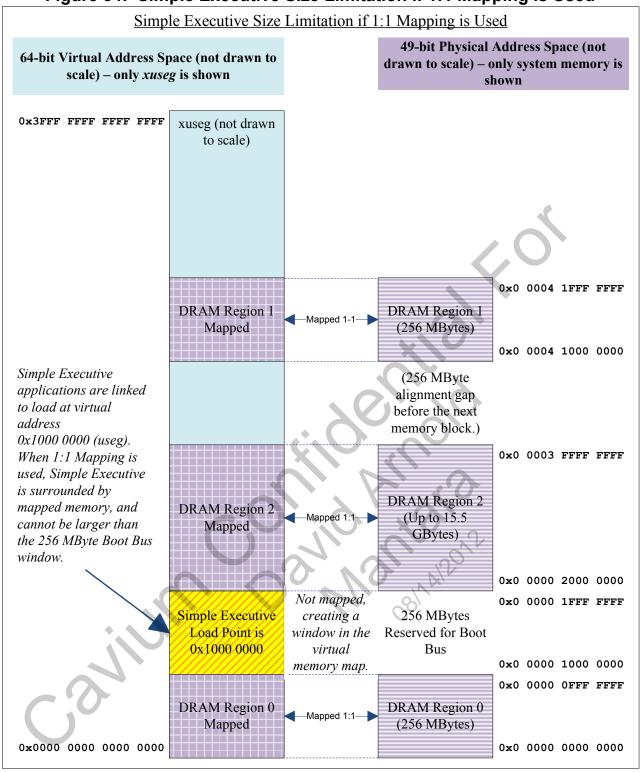

| 14.4.1 CVMX_USE_1_TO_1_TLB_MAPPINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 113 |

| 14.4.2 CVMX_NULL_POINTER_PROTECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 114 |

| 14.5 SE-S 32-Bit Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 114 |

| 15 Linux Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 15.1 Configuring Linux and the Effect on the Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 15.1.1 Linux <i>cvmseg</i> (IOBDMA and Scratchpad) Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 15.1.2 SE-UM 64-Bit: Direct Access to I/O Space Via xkphys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 15.1.3 SE-UM 64-Bit: Direct Access to System Memory Via <i>xkphys</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 15.1.4 SE-UM 32-bit: Reserving a Pool of Free Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 118 |

| 15.2 Linux Kernel Space and Simple Executive API Calls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120 |

| 15.3 Linux Memory Configuration Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 120 |

| 15.4 Linux Kernel-Mode Virtual Address Space on the OCTEON Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 15.5 Linux 64-bit User-Mode Virtual Address Space for OCTEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| 15.6 Linux 32-Bit Virtual Address Space for OCTEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 127 |

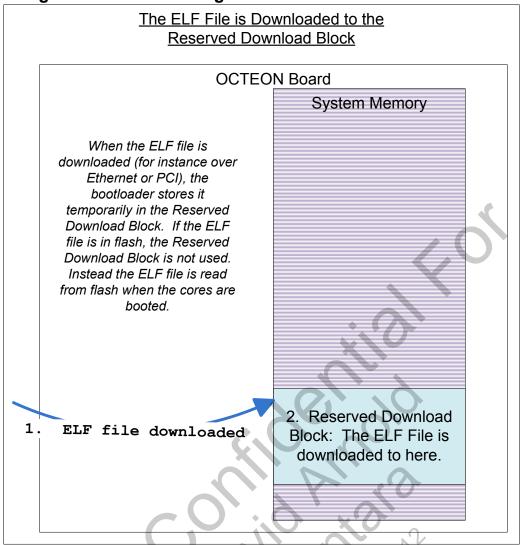

| 16 Downloading and Booting the ELF File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 129 |

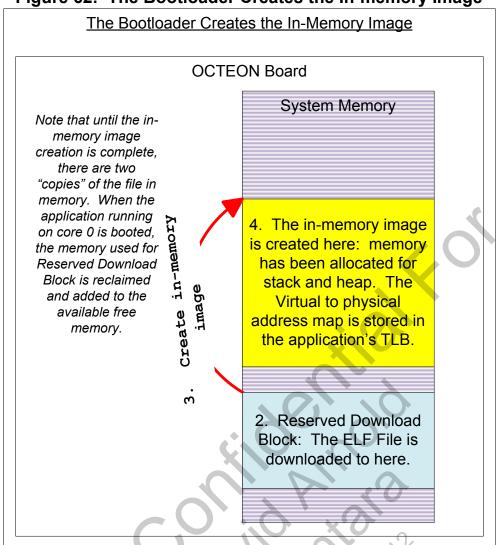

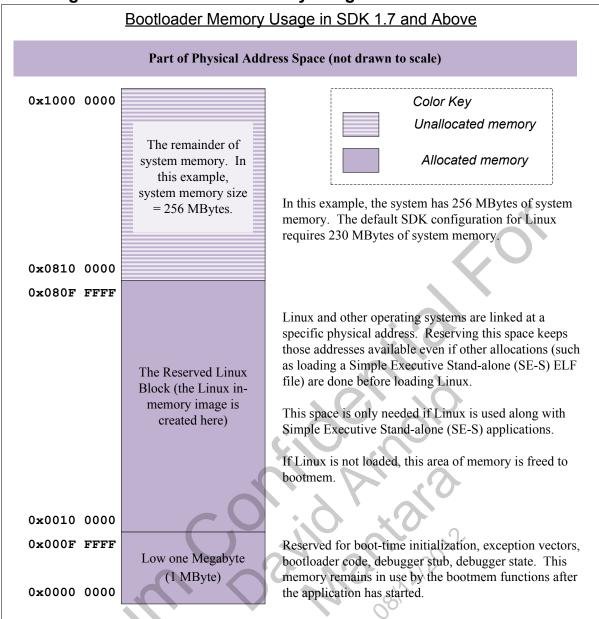

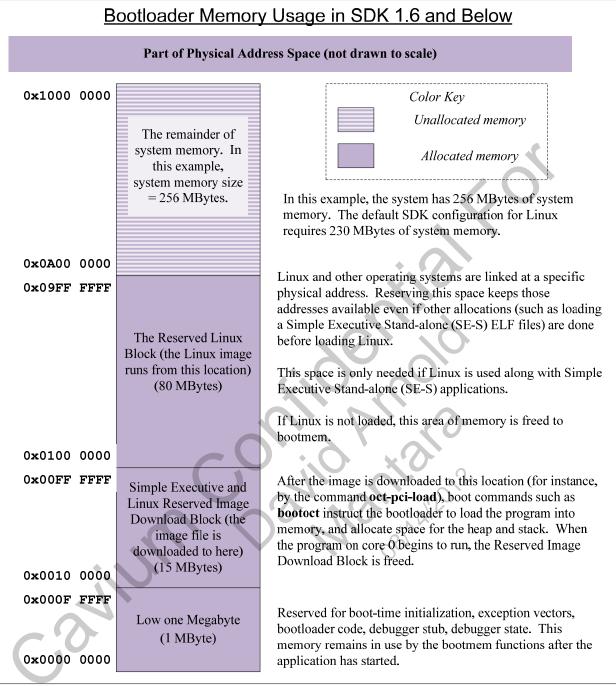

| 16.1 Bootloader Memory Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 130 |

| 16.1.1 The Reserved Download Block 16.1.2 ELF File Maximum Download Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 131 |

| 16.1.2 ELF File Maximum Download Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 131 |

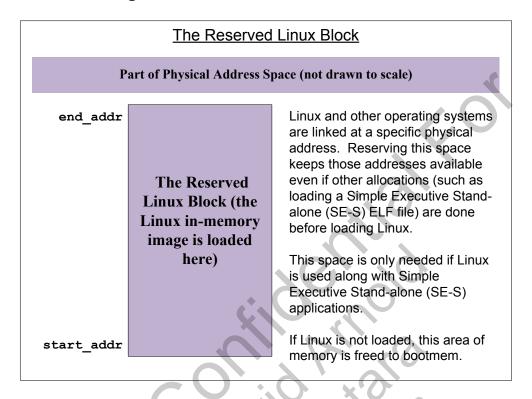

| 16.1.3 The Reserved Linux Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 133 |

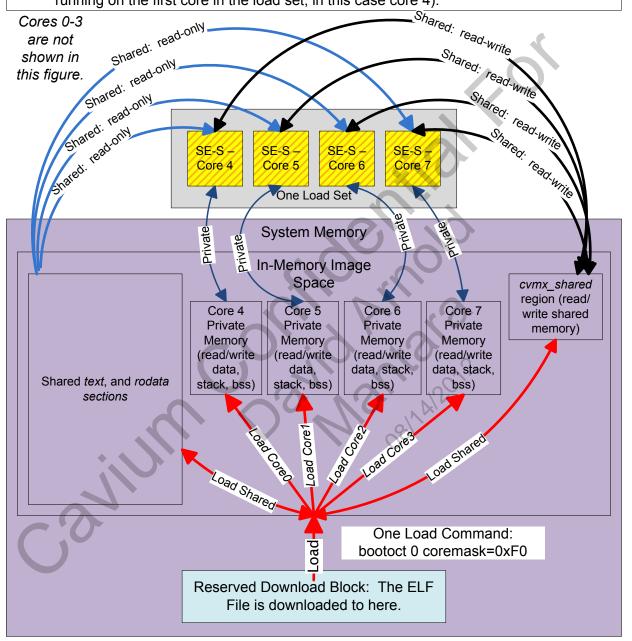

| 16.2 Booting the Same SE-S ELF File on Multiple Cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 135 |

| 16.3 Downloading and Booting Multiple ELF Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

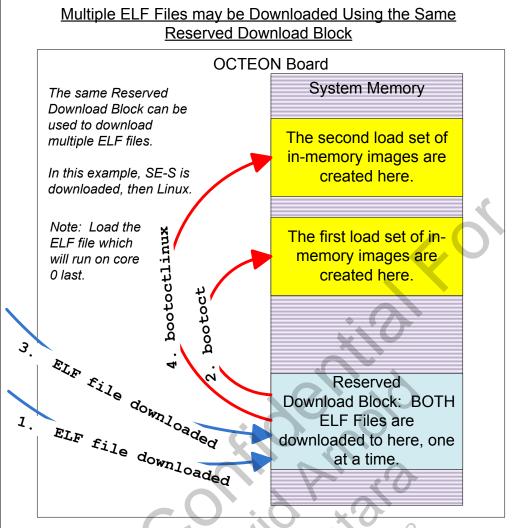

| 16.3.1 Downloading by Re-using One Reserved Download Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

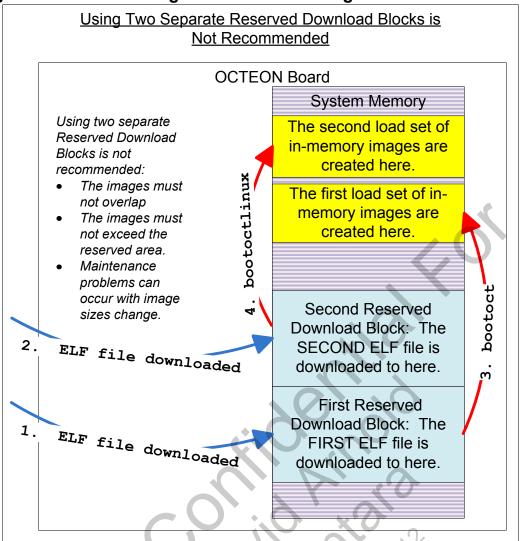

| 16.3.2 Downloading Using Two Different Reserved Download Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 16.4 Protection from Booting Multiple Applications on the Same Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 17.1 Posistan Definitions and Accessing Registrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 140 |

| 17.1 Register Definitions and Accessing Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 140 |

| 17.1.1 Register Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 140 |