## Cavium Networks OCTEON Plus CN50XX Hardware Reference Manual

Contents of this document are subject to change without notice.

The exact features and specifications may change prior to the V1.0 manual revision. CN50XX-HM-0.99E PRELIMINARY Cavium Networks Proprietary and Confidential DO NOT COPY

July 2008

PUBLISHED BY Cavium Networks 805 East Middlefield Road Mountain View, CA 94043 Phone: 650-623-7000 Fax: 650-625-9751 Email: sales@caviumnetworks.com Web: http://www.caviumnetworks.com

#### © 2003-2008 by Cavium Networks

All rights reserved. No part of this manual may be reproduced in any form, or transmitted by any means, without the written permission of Cavium Networks.

Cavium Networks makes no warranty about the use of its products, and reserves the right to change this document at any time, without notice. Whereas great care has been taken in the preparation of this manual, Cavium Networks, the publisher, and the authors assume no responsibility for errors or omissions.

OCTEON<sup>™</sup> is a trademark of Cavium Networks.

MIPS<sup>®</sup> and MIPS64<sup>®</sup> are registered trademarks of MIPS Technologies. cnMIPS<sup>™</sup> is a trademark of MIPS Technologies; Cavium is a licensee of cnMIPS<sup>™</sup>.

All other trademarks or service marks referred to in this manual are the property of their respective owners.

# **Table of Contents**

| Chapte | er 1 |

|--------|------|

|--------|------|

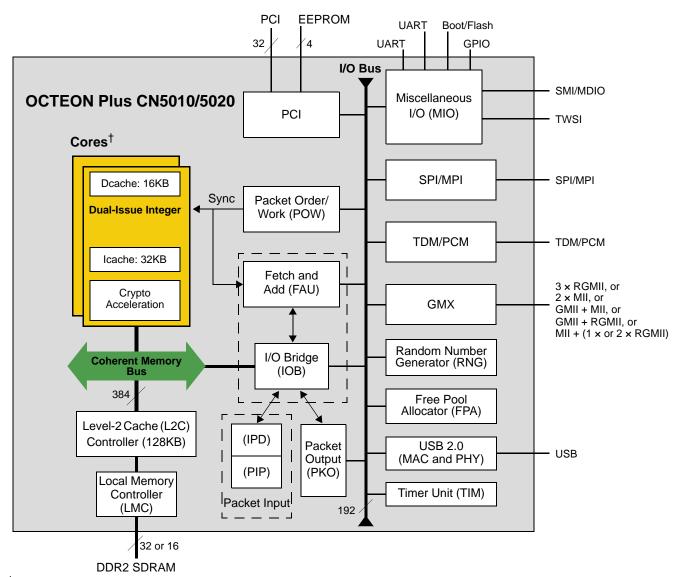

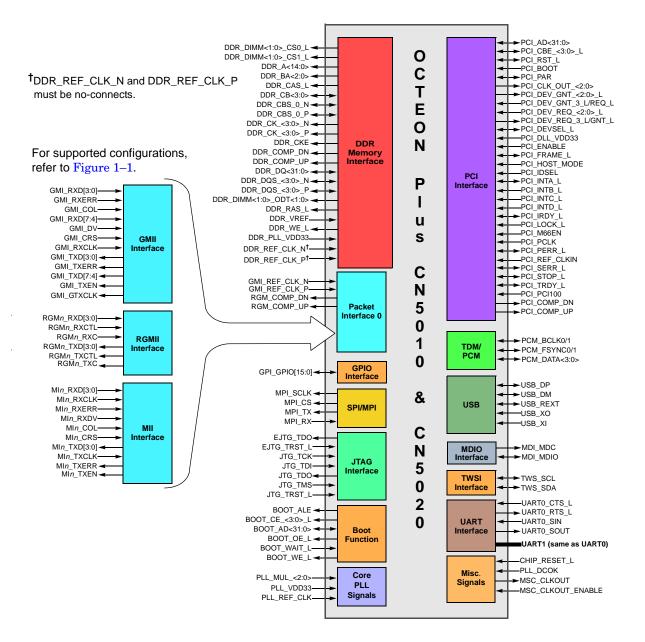

| OCTEO | N Plus CN50XX                                                               |

|-------|-----------------------------------------------------------------------------|

|       | v                                                                           |

| 1.1   | Principles of Operation                                                     |

|       | 1.1.1 CPU Cores                                                             |

|       | 1.1.2 Coherent Multicore and I/O L2/DRAM Sharing                            |

|       | 1.1.3 Core Partitioning                                                     |

|       | 1.1.4 Flexible Packet/Control Interfacing                                   |

|       | 1.1.5 In-line Packet-Processing Hardware Acceleration                       |

|       | 1.1.6 Hardware-Assisted Dynamic Memory Allocation/Deallocation              |

|       | 1.1.7 Hardware Work Queuing, Scheduling, Ordering, and Synchronization      |

|       | 1.1.8 Essential Quality of Service (QoS) Functions Implemented in Hardware. |

|       | 1.1.9 Security Features                                                     |

|       | 1.1.10 Coprocessor Accelerators                                             |

|       | 1.1.11 Debug Support                                                        |

| 1.2   | CN50XX System Applications                                                  |

| 1.3   | Remaining Chapters                                                          |

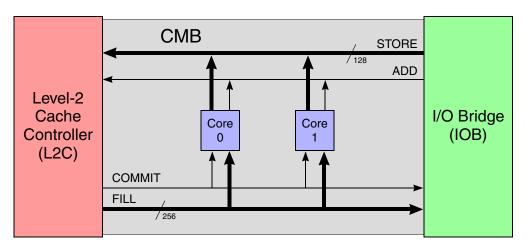

| 1.0   | 1.3.1 Coherent Memory Bus (CMB), Level-Two Cache Controller (L2C),          |

|       | and DRAM Controller                                                         |

|       | 1.3.2 I/O Bus and I/O Bridge                                                |

|       | 1.3.3 CPU Cores                                                             |

|       | 1.3.4 Packet Order / Work Unit (POW)                                        |

|       | 1.3.5 Free Pool Unit (FPA)                                                  |

|       | 1.3.6 Packet Input Processing/Input Packet Data Unit (PIP/IPD)              |

|       | 1.3.7 Packet Output Unit (PKO)                                              |

|       | 1.3.8 PCI Unit                                                              |

|       | 1.3.9 Timer Unit (TIM)                                                      |

|       | 1.3.10 Central Interrupt Unit (CIU)                                         |

|       | 1.3.11 Boot Bus Unit                                                        |

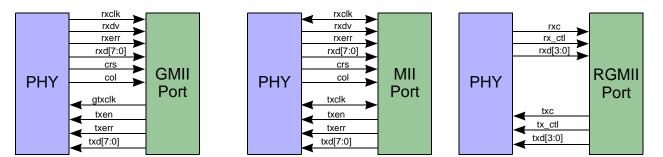

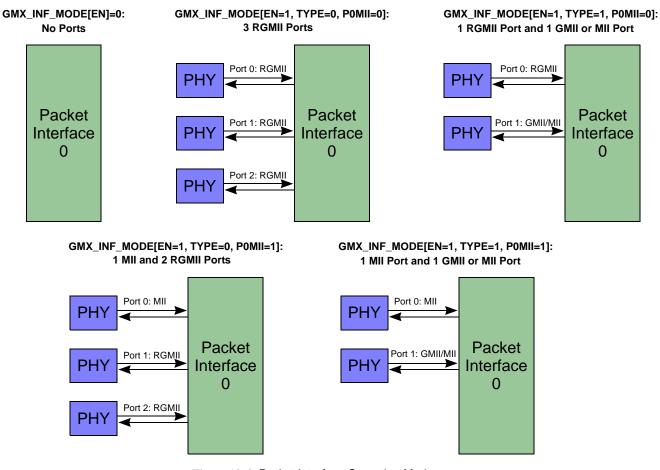

|       | 1.3.12 RGMII/GMII/MII Unit (GMX)                                            |

|       | 1.3.13 TDM/PCM Unit                                                         |

|       | 1.3.14 GPIO Unit                                                            |

|       | 1.3.15 UART Unit                                                            |

|       | 1.3.16 TWSI Unit                                                            |

|       | 1.3.17 System Management Interface (SMI)                                    |

|       | 1.3.18 Random Number Generator (RNG/RNM)                                    |

|       | 1.3.19 SPI/MPI Unit                                                         |

|       | 1.3.20 USB Unit                                                             |

|       | 1.3.21 Electrical Specifications                                            |

|       | 1.3.22 AC Characteristics                                                   |

|       | 1.3.23 Mechanical Specifications                                            |

|       | 1.3.24 Signal Descriptions                                                  |

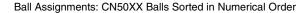

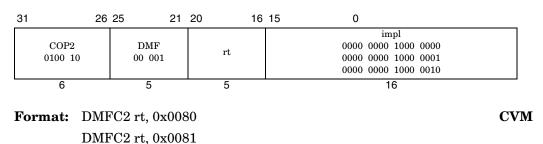

|       | 1.3.25 Ball Assignments                                                     |

| 1.4   | Configuration and Status Registers (CSRs)                                   |

|       | 1.4.1 CSR Field Types                                                       |

| ohere | nt Memory Bus, Level-2 Cache Controller, DRAM Controller                    |

**Chapter 2**

| 2.1.1   | 1 CMB Overview                        |

|---------|---------------------------------------|

| 2.1.2   | 2 CMB Buses                           |

| 2.1.3   | 3 CMB Description                     |

| 2.1.4   |                                       |

| 2.1.    |                                       |

|         |                                       |

|         | rel-2 Cache Controller (L2C)          |

| 2.2.1   |                                       |

| 2.2.2   |                                       |

| 2.2.3   |                                       |

| 2.2.4   | · · · · · · · · · · · · · · · · · · · |

| 2.2.5   | 8                                     |

| 2.2.0   | 6 Cache-Block Flush and Unlocking     |

| 2.2.'   | 7 Memory Input Queue Arbitration      |

| 2.2.8   | 8 COMMIT and FILL Bus Arbitration     |

| 2.2.9   | 9 L2C ECC Codes                       |

| 2.3 DR  | AM Controller (LMC)                   |

| 2.5 D10 |                                       |

|         |                                       |

| 2.3.2   | 8                                     |

| 2.3.3   | · · · · · · · · · · · · · · · · · · · |

| 2.3.4   |                                       |

| 2.3.    |                                       |

| 2.3.0   |                                       |

| 2.3.'   | · · · · ·                             |

| 2.3.8   | 8 DRAM Controller Initialization      |

| 2.3.9   | 9 DDR Clock-Speed Programming Tables  |

| 2.3.1   | 10 DRAM ECC Codes                     |

| 2.4 L20 | C Registers                           |

|         | L2C_CFG                               |

|         | L2T_ERR                               |

|         | L2D_ERR                               |

|         | L2D_FADR                              |

|         | <br>L2D_FSYN0                         |

|         | L2D_FSYN1                             |

|         | L2C_DBG                               |

|         | L2C_LFB0                              |

|         | L2C_LFB1                              |

|         | L2C_LFB2                              |

|         | L2C_LFB3                              |

|         | L2C_DUT                               |

|         | L2C_LCKBASE                           |

|         | L2C_LCKOFF                            |

|         | L2C_SPAR0                             |

|         | L2C_SPAR4                             |

|         | L2C_PFCTL                             |

|         | L2C_PFC(03)                           |

|         | L2D_BST0                              |

|         | L2D_BST1                              |

|         | L2D_BST2                              |

|         | L2D_BST3                              |

|         | L2D_FUS0                              |

|         | L2D_FUS1                              |

|         | L2D_FUS2                              |

|         | L2D_FUS3                              |

|         | L2C_BST0                              |

|         | L2C_BST1                              |

|         | L2C_BST2                              |

| 2.5 LM  | C Registers                           |

|           |          | LMC_MEM_CFG0                                          | 106          |

|-----------|----------|-------------------------------------------------------|--------------|

|           |          | LMC_MEM_CFG1                                          | 109          |

|           |          | LMC_CTL                                               | 111          |

|           |          | LMC_DDR2_CTL                                          | 113          |

|           |          | LMC_FADR                                              | 115          |

|           |          | LMC_COMP_CTL                                          | 115          |

|           |          | LMC_WODT_CTL<br>LMC_ECC_SYND                          | $116 \\ 117$ |

|           |          | LMC_ECC_SIND<br>LMC_IFB_CNT_LO                        | 117          |

|           |          | LMC_IFB_CNT_HI                                        | 118          |

|           |          | LMC_OPS_CNT_LO                                        | 118          |

|           |          | LMC_OPS_CNT_HI                                        | 118          |

|           |          | LMC_DCLK_CNT_LO                                       | 118          |

|           |          | LMC_DCLK_CNT_HI                                       | 119          |

|           |          | LMC_RODT_CTL                                          | 119          |

|           |          | LMC_DELAY_CFG                                         | 119          |

|           |          | LMC_CTL1                                              | 120          |

|           |          | LMC_DUAL_MEMCFG                                       | 121          |

|           |          | LMC_RODT_COMP_CTL                                     | 123          |

|           |          | LMC_PLL_CTL                                           | 123          |

|           |          | LMC_PLL_STATUS                                        | 124          |

|           |          | LMC_BIST_CTL                                          | 124          |

|           |          | LMC_BIST_RESULT                                       | 124          |

| Chapter 3 |          | ing, I/O Bridge (IOB) and                             |              |

|           | Fetch a  | nd Add Unit (FAU)                                     | 125          |

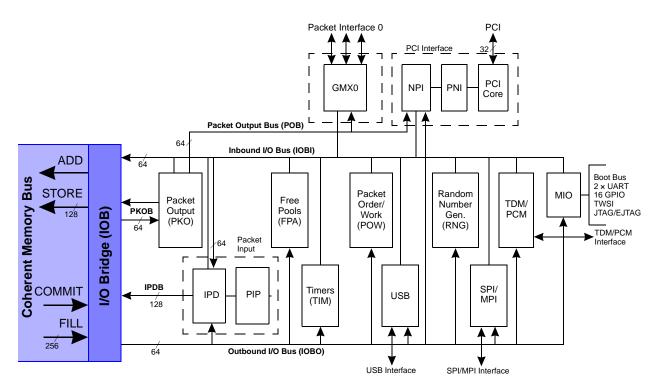

|           | 3.1      | CN50XX I/O Busing                                     | 126          |

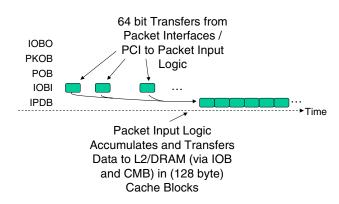

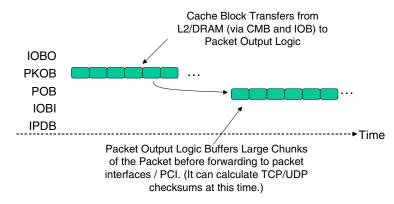

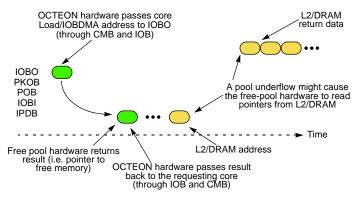

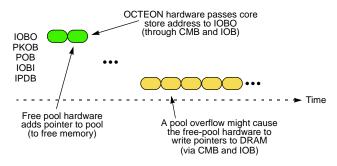

|           |          | 3.1.1 I/O Busing Overview                             | 126          |

|           |          | 3.1.2 I/O Bus Flow Examples                           | 127          |

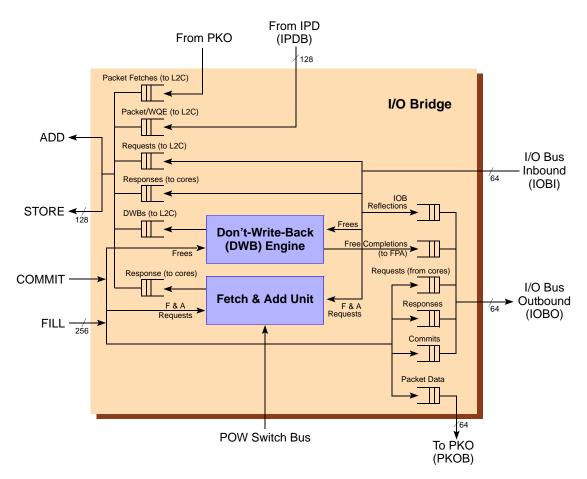

|           | 3.2      | IOB Architecture                                      | 129          |

|           |          | 3.2.1 IOB Architecture Overview                       | 129          |

|           | 3.3      |                                                       | 130          |

|           |          | Don't-Write-Back Engine                               |              |

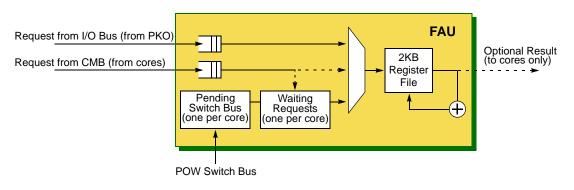

|           | 3.4      | Fetch and Add Unit (FAU)                              | 130          |

|           | 3.5      | Fetch-and-Add Operations                              | 132          |

|           |          | 3.5.1 Load Operations                                 | 132          |

|           |          | 3.5.2 IOBDMA Operations                               | 134          |

|           |          | 3.5.3 Store Operations                                | 136          |

|           | 3.6      | IOB Registers                                         | 137          |

|           |          | IOB_FAU_TIMEOUT                                       | 138          |

|           |          | IOB_CTL_STATUS                                        | 138          |

|           |          | IOB_INT_SUM                                           | 138          |

|           |          | IOB_INT_ENB                                           | 139          |

|           |          | IOB_PKT_ERR                                           | 139          |

|           |          | IOB_INB_DATA_MATCH                                    | 139          |

|           |          | IOB_INB_CONTROL_MATCH                                 | 140          |

|           |          | IOB_INB_DATA_MATCH_ENB                                | 140          |

|           |          | IOB_INB_CONTROL_MATCH_ENB                             | 140          |

|           |          | IOB_OUTB_DATA_MATCH                                   | 140          |

|           |          | IOB_OUTB_CONTROL_MATCH                                | 141          |

|           |          | IOB_OUTB_DATA_MATCH_ENB<br>IOB_OUTB_CONTROL_MATCH_ENB | $141 \\ 141$ |

|           |          | IOB_OUTB_CONTROL_MATCH_ENB<br>IOB_BIST_STATUS         | $141 \\ 142$ |

| Chanter 4 |          |                                                       |              |

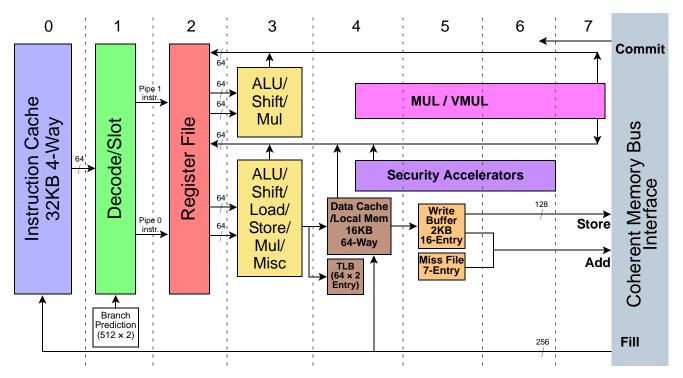

| Chapter 4 |          | ™ Cores                                               | 143          |

|           | Overviev | v                                                     | 144          |

|           | 4.1      | Summary of cnMIPS Core Features                       | 144          |

|           |          | 4.1.1 MIPS64 Version 2.0 Implementation               | 144          |

|           |          | 4.1.2 Cavium-Specific Architectural Additions         | 145          |

|           |          | •                                                     |              |

|      |         | Full Privileged Architecture (i.e. Coprocessor 0) Support14Full EJTAG Version 3.10 Support14 |    |

|------|---------|----------------------------------------------------------------------------------------------|----|

| 4.2  | cnMII   | PS Core Non-Privileged State                                                                 | 18 |

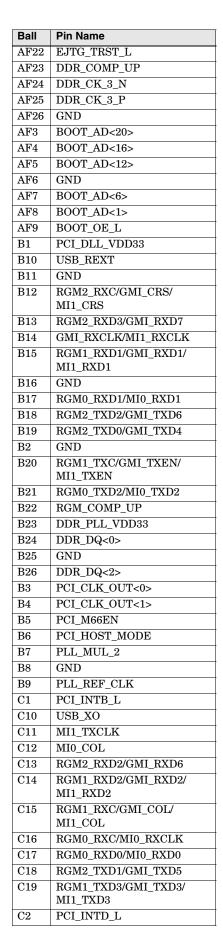

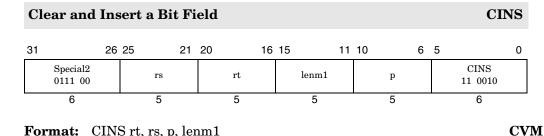

| 4.3  |         | m-Specific Instruction Summary                                                               | 49 |

| 4.4  |         | PS Core Instruction Set Summary                                                              |    |

| 4.5  |         | PS Core Virtual Addresses and CVMSEG                                                         |    |

|      |         |                                                                                              |    |

| 4.6  | -       | cal Addresses                                                                                |    |

| 4.7  |         | MA Operations                                                                                | 50 |

| 4.8  |         | PS Core-Memory Reference Ordering                                                            | 51 |

| 4.9  | cnMII   | PS Core CSR Ordering                                                                         | 52 |

| 4.10 | cnMII   | PS Core Write Buffer                                                                         | 33 |

| 4.11 | cnMII   | PS Core Coprocessor 0 Privileged Registers                                                   | 35 |

|      |         | Index Register                                                                               | 37 |

|      |         | Random Register                                                                              | 37 |

|      |         | EntryLo0, EntryLo1 Registers                                                                 |    |

|      |         | Context Register 16                                                                          |    |

|      |         | PageMask Register                                                                            |    |

|      |         | PageGrain Register       16         Wired Register       16                                  |    |

|      |         | HWREna Register   16                                                                         |    |

|      |         | BadVAddr Register                                                                            |    |

|      |         | Count Register                                                                               | 39 |

|      |         | EntryHi Register                                                                             |    |

|      |         | Compare Register                                                                             |    |

|      |         | Status Register                                                                              |    |

|      |         | IntCtl Register                                                                              |    |

|      |         | SRSCtl Register                                                                              |    |

|      |         | Exception Program Counter                                                                    |    |

|      |         | PRId Register                                                                                |    |

|      |         | EBase Register                                                                               | 12 |

|      |         | Config Register 17                                                                           | 2  |

|      |         | Config1 Register                                                                             |    |

|      |         | Config2 Register                                                                             |    |

|      |         | Config3 Register                                                                             |    |

|      |         | WatchHi Register                                                                             |    |

|      |         | XContext Register                                                                            |    |

|      |         | Debug Register                                                                               |    |

|      |         | Debug Exception Program Counter Register                                                     | 76 |

|      |         | Performance Counter Control Register 17                                                      |    |

|      |         | Performance Counter Counter Register                                                         |    |

|      |         | ErrorEPC 17                                                                                  |    |

|      | 4 1 1 1 | DESAVE Register                                                                              |    |

|      | 4.11.1  | CacheErr (Icache)                                                                            |    |

|      |         | CacheErr (Dcache)                                                                            |    |

|      |         | TagLo Register (Icache)       18                                                             |    |

|      |         | TagLo Register (Dcache)       18                                                             |    |

|      |         | DataLo Register (Icache)                                                                     | 30 |

|      |         | DataLo Register (Dcache)                                                                     |    |

|      |         | TagHi Register   18                                                                          |    |

|      |         | DataHi Register (Icache)                                                                     |    |

|      |         | DataHi Register (Dcache)   18     CvmCtl Register   18                                       |    |

|      |         | CvmMemCtl Register                                                                           |    |

|      |         | CvmCount Register                                                                            |    |

|      |         |                                                                                              |    |

Chapter 5

|     |        | Multicore Debug Register                                                                  | 186        |

|-----|--------|-------------------------------------------------------------------------------------------|------------|

|     | 4.12   | cnMIPS™ Core EJTAG DRSEG Registers                                                        | 186        |

|     |        | Debug Control Register (DCR)                                                              | 187        |

|     |        | Instruction Breakpoint Status (IBS) Register                                              | 187        |

|     |        | Instruction Breakpoint Address (IBA03) Register                                           | 187        |

|     |        | Instruction Breakpoint Address Mask (IBM03) Register                                      | 187        |

|     |        | Instruction Breakpoint ASID (IBASID03) Register                                           | 188        |

|     |        | Instruction Breakpoint Control (IBC03) Register                                           | 188        |

|     |        | Data Breakpoint Status (DBS) Register                                                     | 188        |

|     |        | Data Breakpoint Address (DBA03) Register<br>Data Breakpoint Address Mask (DBM03) Register | 188<br>189 |

|     |        | Data Breakpoint ASID (DBASID03) Register                                                  | 189        |

|     |        | Data Breakpoint Control (DBC03) Register                                                  | 189        |

|     |        | Data Breakpoint Value (DBV03) Register                                                    | 189        |

|     | 1 1 2  | cnMIPS <sup>™</sup> Core EJTAG TAP Registers                                              | 190        |

|     | 4.10   | Device ID Register Format                                                                 | 190        |

|     |        | Implementation Register Format (TAP Instruction IMPCODE)                                  | 190        |

|     |        | Data Register (TAP Instruction DATA, ALL, or FASTDATA)                                    | 191        |

|     |        | Address Register (TAP Instruction ADDRESS or ALL)                                         | 191        |

|     |        | EJTAG Control Register (ECR) (TAP Instruction CONTROL or ALL)                             | 191        |

|     |        | PC Sample Register Format (TAP Instruction PCSAMPLE)                                      | 191        |

|     |        | EJTAG Boot Indication                                                                     | 192        |

|     |        | Bypass Register                                                                           | 192        |

|     |        | Fastdata Register                                                                         | 192        |

|     | 4.14   | cnMIPS Core Pipelines                                                                     | 193        |

|     | 4.15   | Special MUL Topics                                                                        | 194        |

|     |        | COP2 Latencies                                                                            | 196        |

|     |        | cnMIPS Core Hardware Debug Features                                                       | 197        |

|     | 4.17   | 4.17.1 Multicore Debug Support                                                            | 197        |

|     |        | 4.17.2 System Debug Characteristics                                                       | 198        |

|     | 4 10   | cnMIPS Core Load-Linked / Store-Conditional                                               |            |

|     |        |                                                                                           | 200        |

|     |        | cnMIPS Core Exceptions                                                                    | 200        |

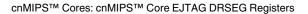

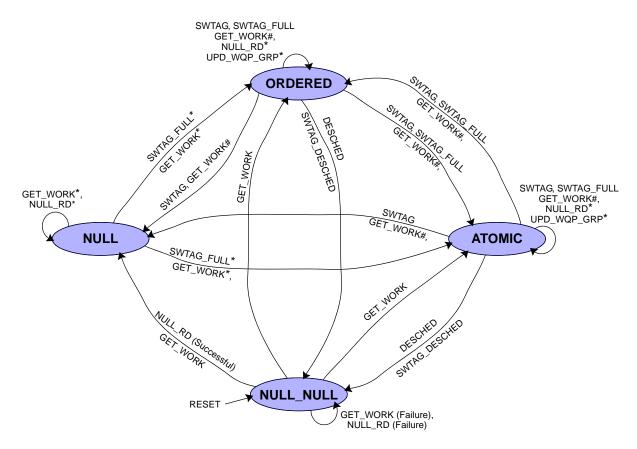

| Pac | cket ( | Order / Work Unit (POW)                                                                   | 205        |

| Ove | erview | ν                                                                                         | 206        |

|     | 5.1    | POW Work Flow, Operations, and Ordering                                                   | 207        |

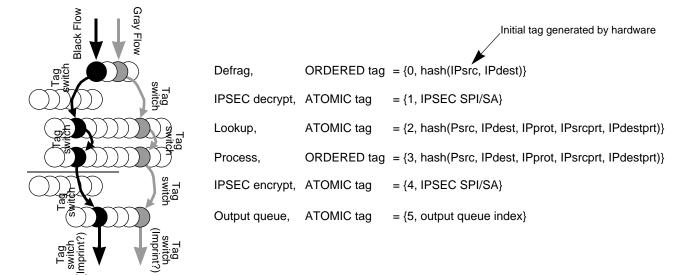

|     | 5.2    | Software Architecture Example                                                             | 213        |

|     | 0.2    | 5.2.1 Defragmentation                                                                     | 216        |

|     |        | 5.2.2 IPSEC Decryption                                                                    | 210        |

|     |        | 5.2.3 Lookup                                                                              | 210        |

|     |        | 5.2.4 Process                                                                             | 210        |

|     |        | 5.2.5 IPSEC Encrypt                                                                       | 217        |

|     |        | 5.2.6 Output Queue                                                                        | 217        |

|     | 5.3    | · · · ·                                                                                   |            |

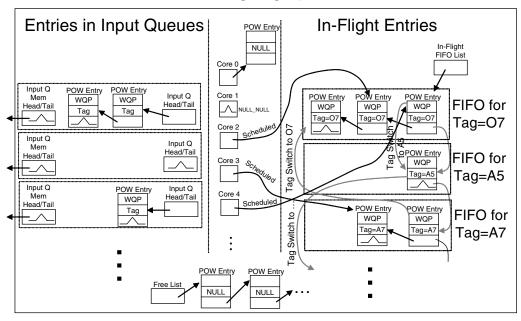

|     |        | POW Internal Architecture                                                                 | 217        |

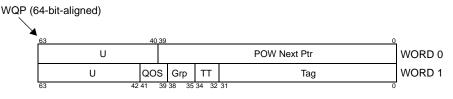

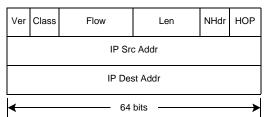

|     | 5.4    | Work-Queue Entry Format                                                                   | 220        |

|     | 5.5    | Core and Fetch-and-Add Pending Switch Bits                                                | 221        |

|     | 5.6    | POW Interrupts                                                                            | 222        |

|     | 5.7    | POW QOS Features                                                                          | 225        |

|     |        | 5.7.1 Thresholds                                                                          | 225        |

|     |        | 5.7.2 Scheduling                                                                          | 225        |

|     | 5.8    | POW Debug Visibility                                                                      | 227        |

|     | 5.9    | POW Performance Considerations                                                            |            |

|     |        |                                                                                           | 228        |

|     |        | Forward Progress Constraints                                                              | 229        |

|     | 5.11   | POW Operations                                                                            | 231        |

|     |        |                                                                                           |            |

|           |          | 5.11.1 Load Operations                                                                 |

|-----------|----------|----------------------------------------------------------------------------------------|

|           |          | 5.11.2 IOBDMA Operations                                                               |

|           |          | 5.11.3 Store Operations                                                                |

|           | 5.12     | POW ECC Codes                                                                          |

|           |          | POW Registers                                                                          |

|           | 0.10     | POW_PP_GRP_MSK0/1                                                                      |

|           |          | POW_WQ_INT_THR(0.15)                                                                   |

|           |          | POW_WQ_INT_CNT(015)                                                                    |

|           |          | POW_QOS_THR(07)                                                                        |

|           |          | POW_QOS_RND(07)                                                                        |

|           |          | POW_WQ_INT                                                                             |

|           |          | POW_WQ_INT_PC                                                                          |

|           |          | POW_NW_TIM                                                                             |

|           |          | POW_ECC_ERR                                                                            |

|           |          | POW_NOS_CNT 249                                                                        |

|           |          | POW_PF_RST_MSK                                                                         |

|           |          | POW_WS_PC(0.15)                                                                        |

|           |          | POW_IQ_CNT(07)                                                                         |

|           |          | POW_WA_COM_PC                                                                          |

|           |          | POW_IQ_COM_CNT                                                                         |

|           |          | POW_TS_PC                                                                              |

|           |          | POW_DS_PC                                                                              |

|           |          | POW_BIST_STAT                                                                          |

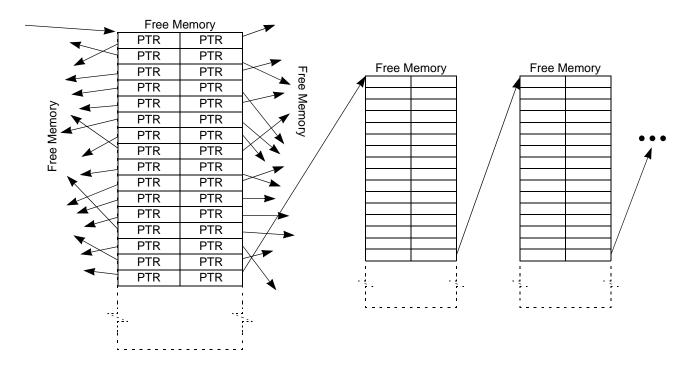

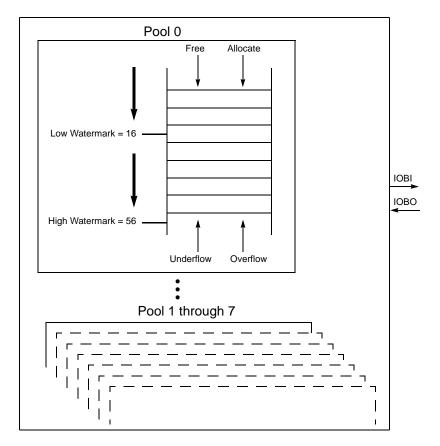

| Chapter 6 | Free Po  | ol Unit (FPA)                                                                          |

|           |          | v                                                                                      |

|           |          |                                                                                        |

|           | 6.1      | Free Pool Unit Operations                                                              |

|           |          | 6.1.1 Load Operations                                                                  |

|           |          | 6.1.2 IOBDMA Operations                                                                |

|           |          | 6.1.3 Store Operations                                                                 |

|           | 6.2      | FPA Registers                                                                          |

|           |          | FPA_INT_SUM                                                                            |

|           |          | FPA_INT_ENB                                                                            |

|           |          | FPA_CTL_STATUS                                                                         |

|           |          | FPA_QUE(07)_AVAILABLE                                                                  |

|           |          | FPA_BIST_STATUS         262           FPA_QUE(07)_PAGE_INDEX         262               |

|           |          | FFA_QUE_EXP                                                                            |

|           |          | FPA_QUE_ACT                                                                            |

| Chapter 7 | Deeket   |                                                                                        |

| Chapter 7 |          |                                                                                        |

|           | Overviev | v                                                                                      |

|           | 7.1      | Input Ports 266                                                                        |

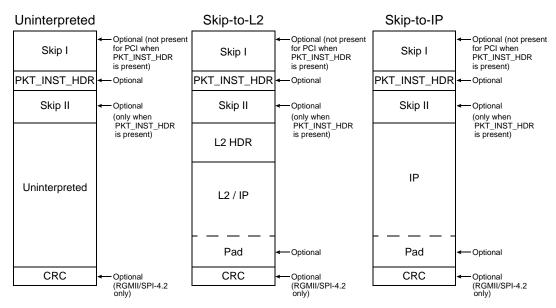

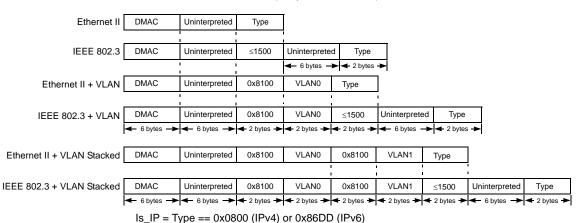

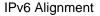

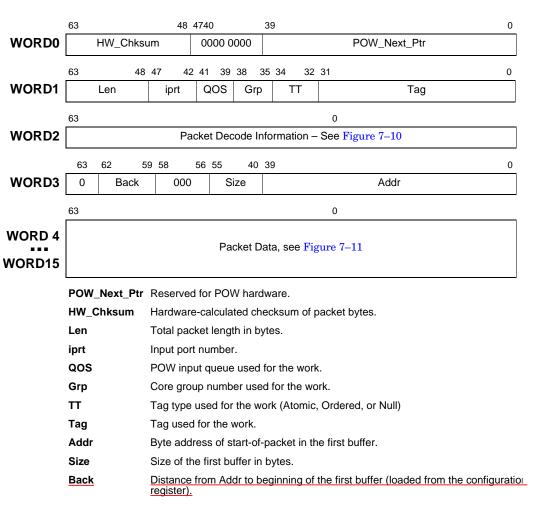

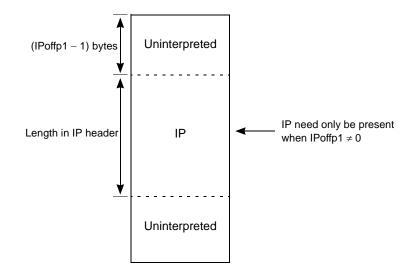

|           | 7.2      | Input Packet Formats and Pre-IP Parsing                                                |

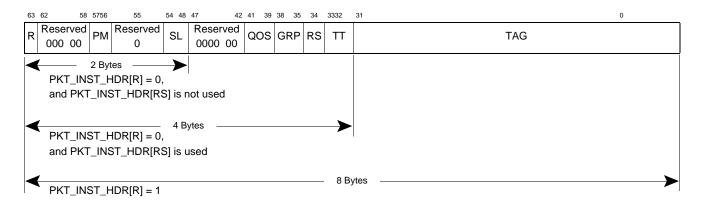

|           |          | 7.2.1 Packet Instruction Header                                                        |

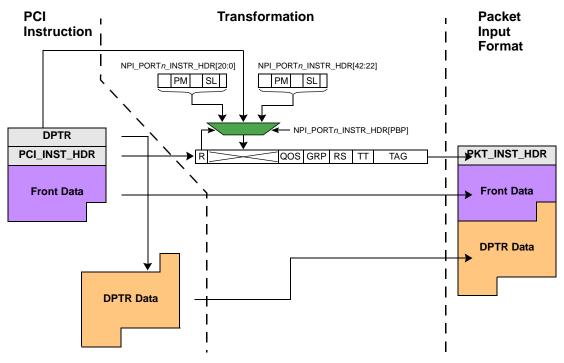

|           |          | 7.2.2 PCI Instruction-to-Packet Conversion                                             |

|           |          | 7.2.3 Parse Mode and Skip Length Selection                                             |

|           |          | 7.2.4 PIP/IPD L2 Parsing and Is_IP Determination                                       |

|           |          | 7.2.5 Pre-IP Parsing Summary                                                           |

|           |          | 7.2.6 Packet Input CRC                                                                 |

|           |          | 7.2.7 Packet Length Checks                                                             |

|           |          | 7.2.8 Legal SKIP Values                                                                |

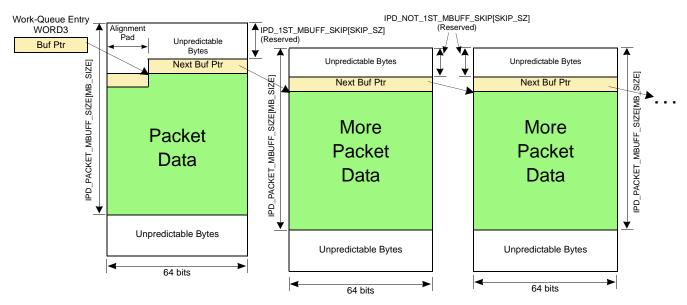

|           | 7.3      | Packet Buffering                                                                       |

|           |          | -                                                                                      |

|           | 7.4      | Packet Scheduling       282         7.4.1       RAWFULL and RAWSCHED Packets       282 |

|           |          |                                                                                        |

|           |          | 7.4.2 QOS                                                                              |

|     | 7.4.3           | Grp                                       | 282 |  |  |

|-----|-----------------|-------------------------------------------|-----|--|--|

|     | 7.4.4           | ТТ                                        | 283 |  |  |

|     | 7.4.5           | Tag                                       | 283 |  |  |

| 7.5 | Work            | -Queue Entry                              | 284 |  |  |

|     |                 |                                           |     |  |  |

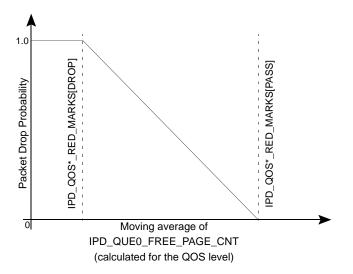

| 7.6 | -               | Packet Data Unit (IPD) Quality of Service | 301 |  |  |

| 7.7 | PIP/I           | PD Per-QOS Admission Control              | 303 |  |  |

| 7.8 | 8 PIP Registers |                                           |     |  |  |

|     |                 | PIP_BIST_STATUS                           | 307 |  |  |

|     |                 | PIP_INT_REG                               | 308 |  |  |

|     |                 | PIP_INT_EN                                | 309 |  |  |

|     |                 | PIP_STAT_CTL                              | 309 |  |  |

|     |                 | PIP_GBL_CTL                               | 310 |  |  |

|     |                 | PIP_GBL_CFG                               | 311 |  |  |

|     |                 | PIP_SFT_RST                               | 312 |  |  |

|     |                 | PIP_IP_OFFSET                             | 313 |  |  |

|     |                 | PIP_TAG_SECRET                            | 313 |  |  |

|     |                 | PIP_TAG_MASK                              | 314 |  |  |

|     |                 | PIP_TODO_ENTRY                            | 314 |  |  |

|     |                 | PIP_DEC_IPSEC(0.3)                        | 314 |  |  |

|     |                 | PIP_RAW_WORD                              | 314 |  |  |

|     |                 | PIP_QOS_VLAN(07)                          | 315 |  |  |

|     |                 | PIP_QOS_WATCH(0.7)                        | 315 |  |  |

|     |                 | PIP_FRM_LEN_CHK0/1                        | 315 |  |  |

|     |                 | PIP_PRT_CFG(0.2, 32/33)                   | 316 |  |  |

|     |                 | PIP_PRT_TAG(0.2, 32/33)                   | 317 |  |  |

|     |                 | PIP_QOS_DIFF(0.63)                        | 318 |  |  |

|     |                 | PIP_TAG_INC(063)                          | 318 |  |  |

|     | 7.8.1           | PIP Statistics Counters                   | 319 |  |  |

|     | 1.0.1           | PIP_STAT0_PRT(0.2, 32/33)                 | 319 |  |  |

|     |                 | PIP_STAT1_PRT(02, 32/33)                  | 319 |  |  |

|     |                 | PIP_STAT2_PRT(02, 32/33)                  | 319 |  |  |

|     |                 | PIP_STAT3_PRT(02, 32/33)                  | 320 |  |  |

|     |                 | PIP_STAT4_PRT(0.2, 32/33)                 | 320 |  |  |

|     |                 | PIP_STAT5_PRT(0.2, 32/33)                 | 320 |  |  |

|     |                 | PIP_STAT6_PRT(02, 32/33)                  | 320 |  |  |

|     |                 | PIP_STAT7_PRT(02, 32/33)                  | 320 |  |  |

|     |                 | PIP_STAT8_PRT(0.2, 32/33)                 | 321 |  |  |

|     |                 | PIP_STAT9_PRT(02, 32/33)                  | 321 |  |  |

|     | 7.8.2           | PIP Inbound Statistics Registers          | 322 |  |  |

|     | 1.0.2           | PIP_STAT_INB_PKTS(0.2, 32/33)             | 322 |  |  |

|     |                 | PIP_STAT_INB_OCTS(0.2, 32/33)             | 322 |  |  |

|     |                 | PIP_STAT_INB_ERRS(0.2, 32/33)             | 322 |  |  |

|     |                 |                                           |     |  |  |

| 7.9 | IPD I           | Registers                                 | 323 |  |  |

|     |                 | IPD_1ST_MBUFF_SKIP                        | 324 |  |  |

|     |                 | IPD_NOT_1ST_MBUFF_SKIP                    | 324 |  |  |

|     |                 | IPD_PACKET_MBUFF_SIZE                     | 324 |  |  |

|     |                 | IPD_CTL_STATUS                            | 325 |  |  |

|     |                 | IPD_WQE_FPA_QUEUE                         | 326 |  |  |

|     |                 | IPD_PORT(02, 32/33)_BP_PAGE_CNT           | 326 |  |  |

|     |                 | IPD_SUB_PORT_BP_PAGE_CNT                  | 326 |  |  |

|     |                 | IPD_1ST_NEXT_PTR_BACK                     | 327 |  |  |

|     |                 | IPD_2ND_NEXT_PTR_BACK                     | 327 |  |  |

|     |                 | IPD_INT_ENB                               | 327 |  |  |

|     |                 | IPD_INT_SUM                               | 328 |  |  |

|     |                 | IPD_SUB_PORT_FCS                          | 328 |  |  |

|     |                 | IPD_QOS(0.7)_RED_MARKS                    | 328 |  |  |

|     |                 | IPD_PORT_BP_COUNTERS_PAIR(02, 32/33)      | 329 |  |  |

|     |                 | IPD_RED_PORT_ENABLE                       | 329 |  |  |

|           | IPD_RED_QUE(07)_PARAM                                   | 330   |

|-----------|---------------------------------------------------------|-------|

|           | IPD_PTR_COUNT                                           | 330   |

|           | IPD_BP_PRT_RED_END                                      |       |

|           | IPD_QUE0_FREE_PAGE_CNT                                  |       |

|           | IPD_CLK_COUNT                                           |       |

|           | IPD_PWP_PTR_FIFO_CTL                                    |       |

|           | IPD_PRC_HOLD_PTR_FIFO_CTL                               |       |

|           | IPD_PRC_PORT_PTR_FIFO_CTL<br>IPD_PKT_PTR_VALID          |       |

|           | IPD_WQE_PTR_VALID                                       |       |

|           | IPD_BIST_STATUS                                         |       |

| Chapter 9 |                                                         |       |

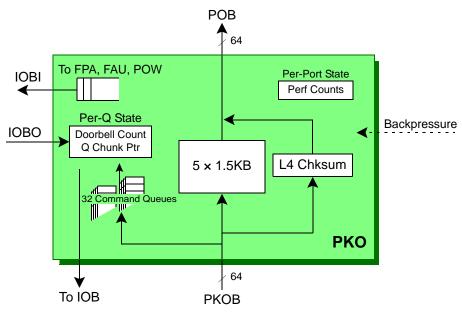

| Chapter 8 | Packet Output Processing Unit (PKO)                     |       |

|           | Overview                                                |       |

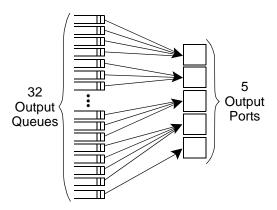

|           | 8.1 Output Ports                                        | 337   |

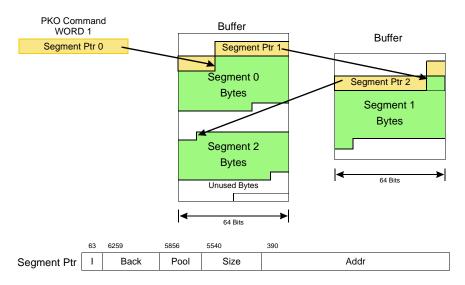

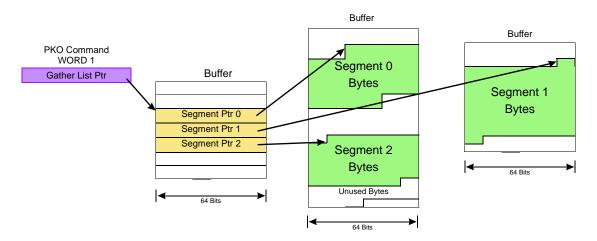

|           | 8.2 Output Packet Format and TCP/UDP Checksum Insertion | 338   |

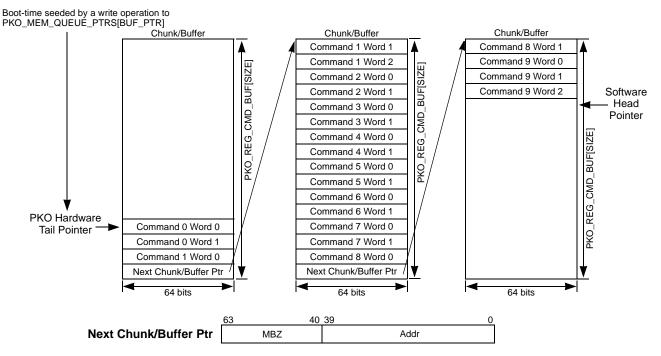

|           | 8.3 PKO Output Queue                                    | 339   |

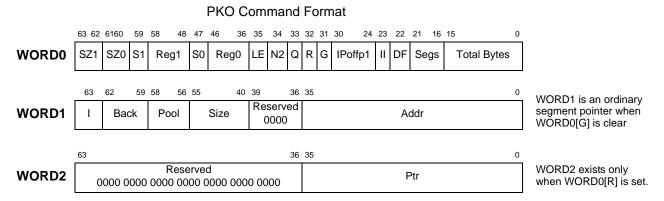

|           | 8.4 PKO Commands                                        |       |

|           |                                                         |       |

|           | 8.5 PKO Queue Arbitration Algorithm                     |       |

|           | 8.6 PKO Don't-Write-Back (DWB) Calculation              | 348   |

|           | 8.7 PKO Performance                                     | 349   |

|           | 8.8 PKO Operations                                      | 349   |

|           | 8.8.1 Store Operations                                  | 349   |

|           | 8.9 PKO Registers                                       |       |

|           | PKO REG FLAGS                                           |       |

|           | PKO_REG_READ_IDX                                        |       |

|           | PKO_REG_CMD_BUF                                         |       |

|           | PKO_REG_GMX_PORT_MODE                                   |       |

|           | PKO_REG_QUEUE_MODE                                      | 353   |

|           | PKO_REG_BIST_RESULT                                     | 353   |

|           | PKO_REG_ERROR                                           |       |

|           | PKO_REG_INT_MASK                                        |       |

|           | PKO_REG_DEBUG0                                          |       |

|           | PKO_REG_DEBUG1                                          |       |

|           | PKO_REG_DEBUG2                                          |       |

|           | PKO_REG_DEBUG3<br>PKO REG QUEUE PTRS1                   |       |

|           | PKO_MEM_QUEUE_PTRS                                      |       |

|           | PKO_MEM_QUEUE_QOS                                       |       |

|           | PKO_MEM_COUNT0                                          |       |

|           | PKO_MEM_COUNT1                                          |       |

|           | PKO_MEM_DEBUG0                                          | 358   |

|           | PKO_MEM_DEBUG1                                          |       |

|           | PKO_MEM_DEBUG2                                          |       |

|           | PKO_MEM_DEBUG3                                          |       |

|           | PKO_MEM_DEBUG4                                          |       |

|           | PKO_MEM_DEBUG5                                          |       |

|           | PKO_MEM_DEBUG6                                          |       |

|           | PKO_MEM_DEBUG7<br>PKO_MEM_DEBUG8                        |       |

|           | PKO_MEM_DEBUG9                                          |       |

|           | PKO_MEM_DEBUG10                                         |       |

|           | PKO_MEM_DEBUG10                                         |       |

|           | PKO_MEM_DEBUG12                                         |       |

|           | PKO_MEM_DEBUG13                                         |       |

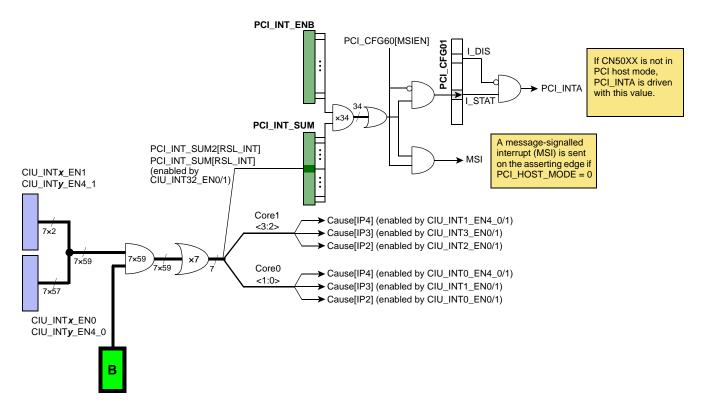

| Chapter 9 | PCI Bus                                                 | . 365 |

|           |                                                         |       |

|           | Overview                                                | 366   |

| 9.1   | CN50XX PCI Features                                                     | 366                                       |

|-------|-------------------------------------------------------------------------|-------------------------------------------|

| 9.2   | CN50XX Addressing as a PCI Target                                       | 367                                       |

|       | 9.2.1 BAR0 - Memory-Mapped CSR Region                                   | 367                                       |

|       | 9.2.2 BAR1 - 32-Bit Memory-Mapped Region                                | 368                                       |

|       | 9.2.3 BAR2 - 64-bit Memory-Mapped Region                                | 370                                       |

|       | 9.2.4 Expansion ROM                                                     | 371                                       |

| 9.3   | PCI Instruction Input From an External Host                             | 371                                       |

|       | 9.3.1 PCI Instruction Format                                            | 371                                       |

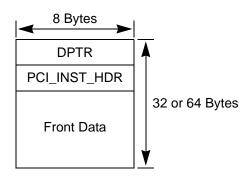

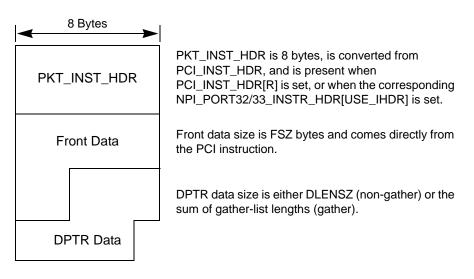

|       | 9.3.2 PCI Input Packet                                                  | 373                                       |

|       | 9.3.3 DPTR Formats                                                      | 375                                       |

| 9.4   | PCI Packet Output From CN50XX                                           | 377                                       |

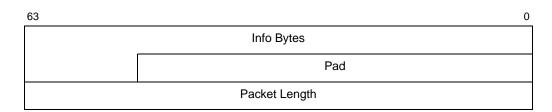

|       | 9.4.1 Info-Pointer Mode                                                 | 379                                       |

|       | 9.4.2 Buffer-Pointer-Only Mode                                          | 380                                       |

| 9.5   | PCI DMA Engine Access From Cores                                        | 381                                       |

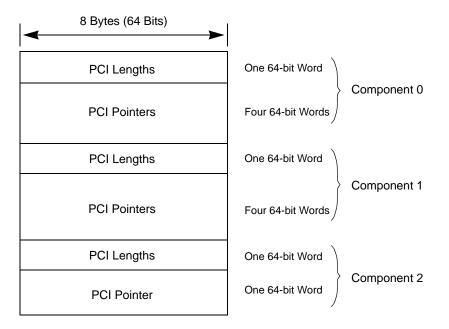

|       | 9.5.1 PCI DMA Instruction-Header Format                                 | 382                                       |

|       | 9.5.2 PCI DMA Instruction Local-Pointer Format                          | 383                                       |

|       | 9.5.3 PCI DMA Instruction PCI Components and Processing                 | 385                                       |

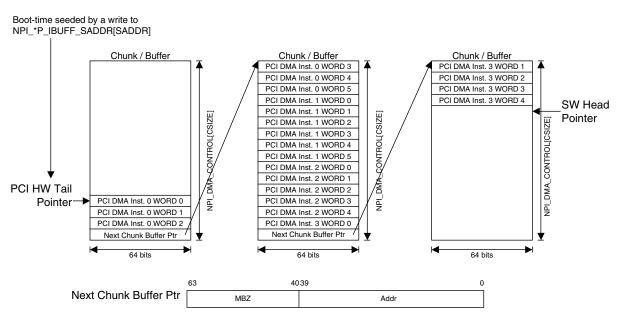

|       | 9.5.4 PCI DMA Instruction Fetching                                      | 386                                       |

|       | 9.5.5 PCI DMA Instruction Ordering and Completion                       | 387                                       |

|       | 9.5.6 PCI DMA Engine Don't-Write-Back Calculation                       | 388                                       |

|       | 9.5.7 Host Output Queueing Via the PCI DMA Engine                       | 388                                       |

| 9.6   | PCI Memory Space Loads/Stores to BAR1/2                                 | 389                                       |

|       | 9.6.1 Referencing L2/DRAM With CN50XX as a PCI Target                   | 389                                       |

| 9.7   | CN50XX PCI Internal Arbiter                                             | 391                                       |

| 9.8   | CN50XX PCI MSI Support                                                  | 391                                       |

|       | ••                                                                      |                                           |

| 9.9   | Endian Swapping<br>9.9.1 PASS_THRU MODE (== 0)                          | $391 \\ 391$                              |

|       | 9.9.1 FASS_THK0 MODE (== 0)<br>9.9.2 64b_BYTE_SWAP Mode (== 1)          | 391<br>392                                |

|       | 9.9.3 32b_BYTE_SWAP Mode (== 2)                                         | 393                                       |

|       | 9.9.4 32b_LW_SWAP Mode (== 3)                                           | 393                                       |

| 0 10  |                                                                         |                                           |

| 9.10  | PC Bus Operations<br>9.10.1 Load/Store Operations                       | $\frac{394}{394}$                         |

|       | 9.10.2 IOBDMA Operations                                                | 394<br>394                                |

|       | 9.10.2 RSL Access Space (SubDID == 0)                                   | $394 \\ 394$                              |

|       | 9.10.4 PCI Config / IACK / Special Space (SubDID == 1)                  | 395                                       |

|       | 9.10.5 PCI I/O Space (SubDID == 2)                                      | 396                                       |

|       | 9.10.6 Memory Space (SubDID == 3, 4, 5, 6)                              | 396                                       |

|       | 9.10.7 PCI-Related, NCB-Direct, PCICONFIG, and PCI_NCB CSR Access (SubD |                                           |

|       | 7)                                                                      |                                           |

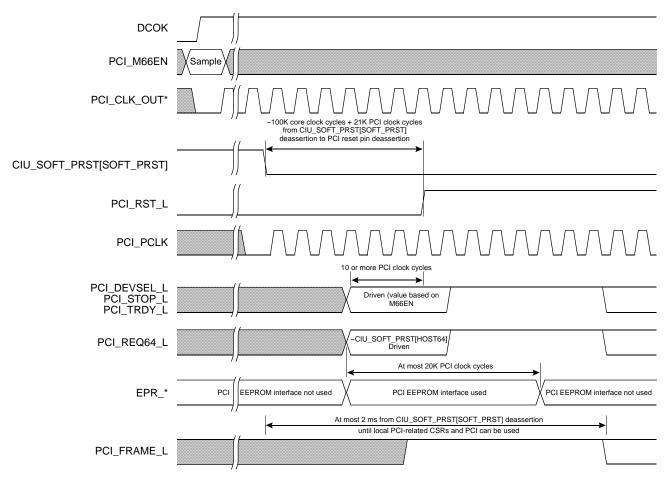

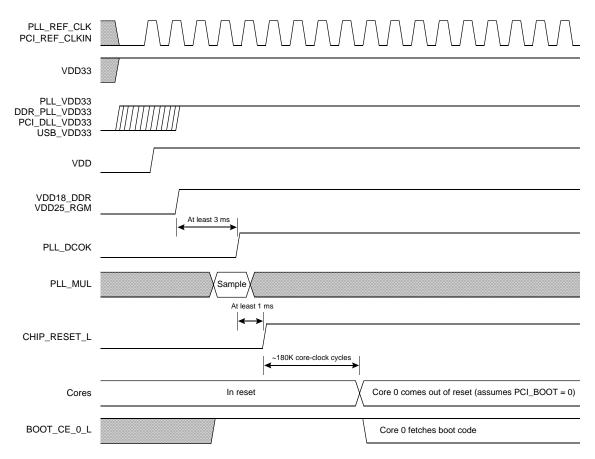

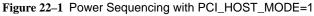

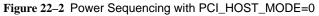

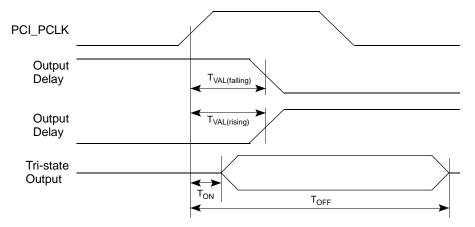

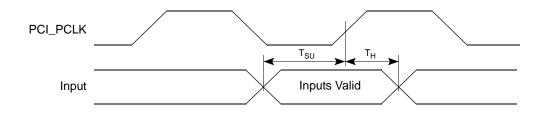

| 9.11  | PCI Reset Sequence                                                      | 397                                       |

| 0.11  | 9.11.1 PCI Reset Sequence in Host Mode                                  | 397                                       |

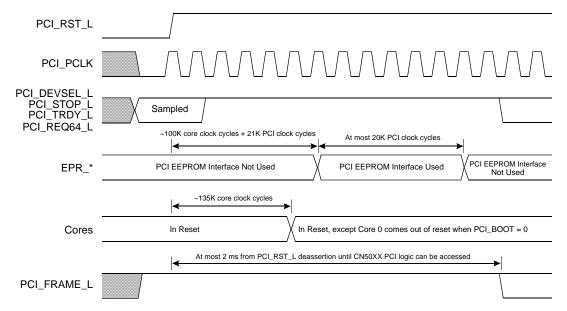

|       | 9.11.2 PCI Reset Sequence in Non-Host Mode                              | 399                                       |

| 9 1 2 | PCI Checklist                                                           | 401                                       |

|       |                                                                         |                                           |

| 9.13  | PCI Configuration Registers                                             | 403                                       |

|       | PCI_CFG00<br>PCI_CFG01                                                  | $\begin{array}{c} 404 \\ 404 \end{array}$ |

|       | PCI_CFG02                                                               | 404                                       |

|       | PCI_CFG03                                                               | 405                                       |

|       | PCI_CFG04                                                               | 405                                       |

|       | PCI_CFG05                                                               | 405                                       |

|       | PCI_CFG06                                                               | 406                                       |

|       | PCI_CFG07                                                               | 406                                       |

|       | PCI_CFG08                                                               | 406                                       |

|       | PCI_CFG09                                                               | 406                                       |

|                        | 406        |

|------------------------|------------|

|                        | 407        |

|                        | 407        |

| =                      | 407        |

| =                      | 407        |

| =                      | 408        |

|                        | 409        |

|                        | 409        |

| =                      | 410        |

|                        | 411        |

| =                      | 411        |

|                        | 412        |

|                        | 413        |

|                        | 413        |

|                        | 414        |

| =                      | 414        |

| =                      | 414        |

| PCI_CFG63              | 414        |

| 9.14 PCI Bus Registers | 415        |

|                        | 417        |

|                        | 417        |

|                        | 417        |

|                        | 418        |

|                        | 418        |

|                        | 419        |

|                        | 422        |

|                        | 423        |

|                        | 424        |

|                        | 426        |

|                        | 426        |

|                        | 426<br>426 |

|                        | 420        |

|                        | 427        |

|                        | 427        |

|                        | 427        |

|                        |            |

|                        | 429        |

|                        | 429        |

|                        | 430        |

|                        | 430        |

|                        | 430        |

|                        | 430        |

|                        | 431        |

|                        | 431<br>431 |

|                        |            |

|                        | 431        |

|                        | 431        |

| 8                      | 432        |

|                        | 433        |

|                        | 433        |

|                        | 434        |

|                        | 434        |

|                        | 436        |

|                        | 438        |

| NPI_PCI_READ_CMD       | 438        |

| NPI_NUM_DESC_OUTPUT0/1 | 438        |

|                        | 439        |

|                        | 439        |

|                        | 439        |

|                        | 439        |

|                        |            |

|            |              | NPI_PCI_BURST_SIZE                          | 440                                       |

|------------|--------------|---------------------------------------------|-------------------------------------------|

|            |              | NPI_BUFF_SIZE_OUTPUT0/1                     | 440                                       |

|            |              | NPI_OUTPUT_CONTROL                          | 441                                       |

|            |              | NPI_LOWP_IBUFF_SADDR                        | 441                                       |

|            |              | NPI_HIGHP_IBUFF_SADDR                       | 441                                       |

|            |              | NPI_LOWP_DBELL<br>NPI_HIGHP_DBELL           | $\begin{array}{c} 442 \\ 442 \end{array}$ |

|            |              | NPI_DMA_CONTROL                             | 442                                       |

|            |              | NPI_PCI_INT_ARB_CFG                         | 443                                       |

|            |              | NPI_INPUT_CONTROL                           | 444                                       |

|            |              | NPI_DMA_LOWP_COUNTS                         | 444                                       |

|            |              | NPI_DMA_HIGHP_COUNTS                        | 444                                       |

|            |              | NPI_DMA_LOWP_NADDR                          | 445                                       |

|            |              | NPI_DMA_HIGHP_NADDR                         | 445                                       |

|            |              | NPI_P0/1_PAIR_CNTS                          | 445                                       |

|            |              | NPI_P0/1_DBPAIR_ADDR                        | 445                                       |

|            |              | NPI_P0/1_INSTR_CNTS                         | 446                                       |

|            |              | NPI_P0/1_INSTR_ADDR                         | 446                                       |

|            |              | NPI_WIN_READ_TO<br>DBG_DATA                 | $\begin{array}{c} 446 \\ 446 \end{array}$ |

|            |              | NPI_PORT_BP_CONTROL                         | 440                                       |

|            |              | NPI PORT32/33 INSTR_HDR                     | 447                                       |

|            |              | NPI_BIST_STATUS                             | 448                                       |

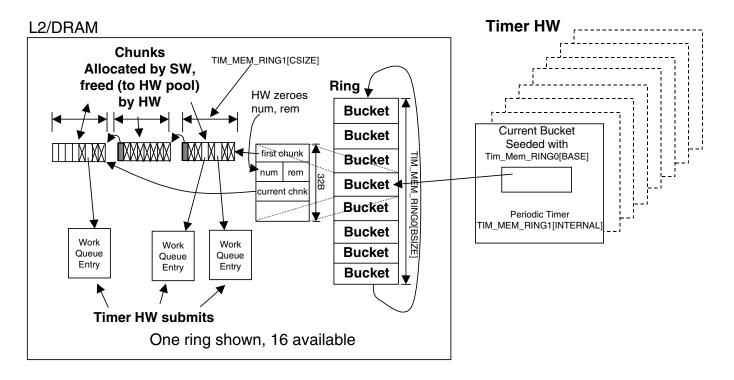

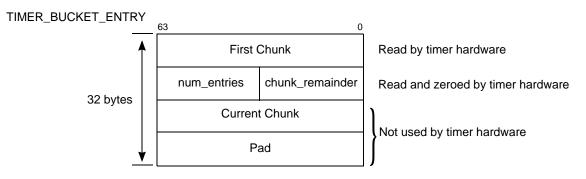

| Chapter 10 | Timer        |                                             | 449                                       |

|            |              |                                             |                                           |

|            |              | _                                           | 450                                       |

|            | 10.1 Tin     | ner Features                                | 450                                       |

|            | 10.2 Tin     | ner Support                                 | 451                                       |

|            | 10.3 Sof     | tware Responsibilities                      | 452                                       |

|            | 10.4 Tin     | ner Registers                               | 454                                       |

|            |              | TIM_REG_FLAGS                               | 455                                       |

|            |              | TIM_REG_READ_IDX                            | 455                                       |

|            |              | TIM_REG_BIST_RESULT                         | 455                                       |

|            |              | TIM_REG_ERROR                               | 456                                       |

|            |              | TIM_REG_INT_MASK                            | 456                                       |

|            |              | TIM_MEM_RING0                               | 456                                       |

|            |              | TIM_MEM_RING1                               | 457                                       |

|            |              | TIM_MEM_DEBUG0                              | 457                                       |

|            |              | TIM_MEM_DEBUG1<br>TIM_MEM_DEBUG2            | $457 \\ 458$                              |

| 01         | 0            |                                             |                                           |

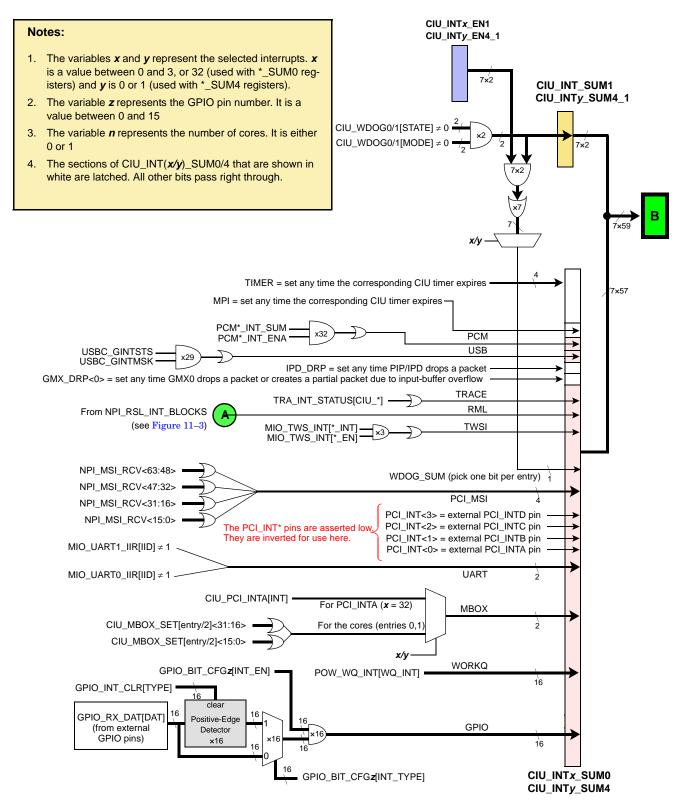

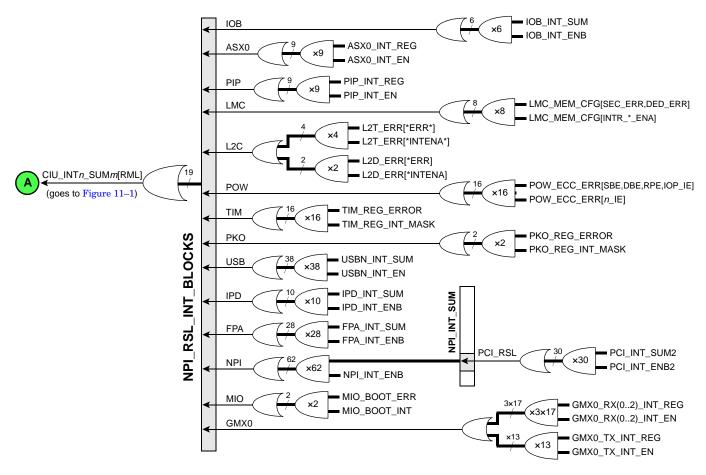

| Chapter 11 | Central Inte | rrupt Unit (CIU)                            | 459                                       |

|            | Overview     |                                             | 460                                       |

|            | 11.1 Cer     | ntral Interrupt Collection and Distribution | 460                                       |

|            | 11.2 Per     | -Core Mailbox Registers                     | 464                                       |

|            |              | -Core Watchdog Timers                       | 465                                       |

|            |              | ur General Timers                           | 466                                       |

|            |              |                                             |                                           |

|            |              | e Availability and Reset                    | 467                                       |

|            | 11.6 Con     | e Debug-Mode Observability                  | 467                                       |

|            | 11.7 Con     | e Debug-Interrupt Generation                | 468                                       |

|            | 11.8 Con     | e Non-Maskable Interrupt Generation         | 468                                       |

|            |              | p Soft-Reset Initiation                     | 468                                       |

|            |              | J Registers                                 | 469                                       |

|            | 11.10010     | CIU INT(03,32) SUM0                         | 409<br>470                                |

|            |              | CIU_INT_SUM1                                | 470                                       |

|            |              | CIU_INT(0.3,32)_EN0                         | 471                                       |

|            |              | CIU_INT(0.3,32)_EN1                         | 471                                       |

|            |              |                                             |                                           |

| Citu INT01_EN4_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | CIU_INT0/1_SUM4                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------|

| Cli TIMO.3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            | CIU_INT0/1_EN4_0                        |

| CIU_WDCG01 474<br>CIU_PP_OKE01 475<br>CIU_MBOX_SET01 475<br>CIU_MBOX_SET01 475<br>CIU_PR_ST 475<br>CIU_PP_BST 475<br>CIU_PP_BST 475<br>CIU_PP_BST 475<br>CIU_PP_BST 475<br>CIU_PP_BST 475<br>CIU_SOFT_BST 475<br>CIU_SOFT_BST 475<br>CIU_SOFT_BST 475<br>CIU_SOFT_RST 475<br>CIUSOFT_CIUSOFT_CIUSOFT<br>CIUSOFT_CIUSOFT<br>CIUSOFT_CIUSOFT<br>CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT 475<br>CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_ST 475<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSOFT_CIUSOFT_55<br>CIUSOFT_CIUSO                                                                                                                                 |            |                                         |

| CIU_PP_POKE01 473<br>CIU_MBOX_CLR01 475<br>CIU_MBOX_CLR01 475<br>CIU_PD_BST 475<br>CIU_PD_BG 475<br>CIU_PD_BG 475<br>CIU_PD_BG 475<br>CIU_USOP — 475<br>CIU_USOP — 475<br>CIU_USOP — 476<br>CIU_USOF _ BIST 476<br>CIU_SOFT _ BIST 477<br>CIU_SOFT _ BIST 477<br>CIU_SOFT _ PRST 477<br>CIU_SOFT _ CIUSA 477<br>CIU_SOFT _ CIUSA 477<br>CIUSA |            |                                         |

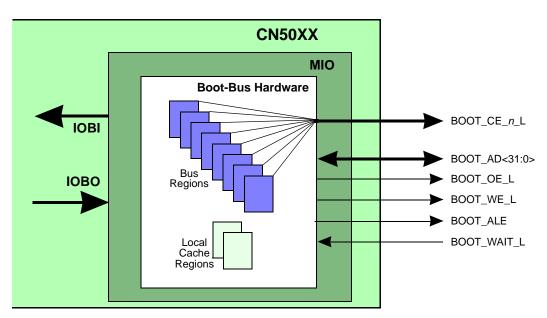

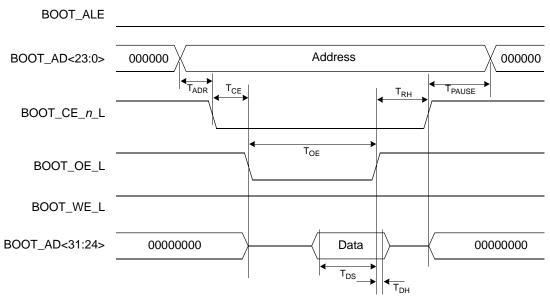

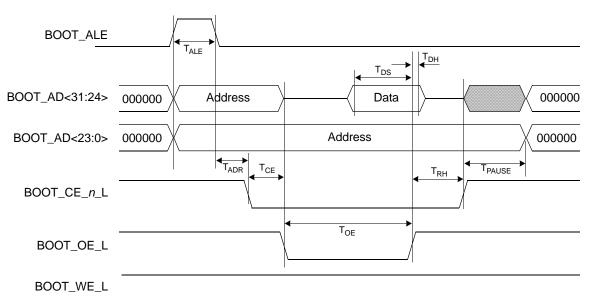

| CIU_MBOX_SET0/1       475         CIU_MBOX_CLR01       475         CIU_PP_RST       475         CIU_PP_RST       475         CIU_PP_RST       476         CIU_PD_RST       476         CIU_DINT       476         CIU_DINT       476         CIU_DINT       476         CIU_SOT       476         CIU_SOT       477         Overview       480         12.1       Boot Bus Address Matching and Regions       481         12.2       Boot Bus Reset Configuration and Booting       482         12.4       Static-Timed Write Sequences       495         12.4       Static-Timed Write Sequences       499         12.4       Static-Timed Mage-Read Sequences       499         12.7       Doot Bus Operations       500         12.7       Ioad Operations       501      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                                         |

| CIU_MBOX_CLR01 475<br>CIU_P DBG 475<br>CIU_P DBG 475<br>CIU_GSTOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                                         |