# Packet Input Processor (PIP) and Input Packet Data (IPD) Units

#### **Revision History**

#### **Revision2 - Nov. 19, 2010**

1. Changed chapter number from 4 to 6.

2. Changed references to the *Configuration and Advanced Topics* chapter: these are two separate chapters now.

3. Added references to new *Essential Topics* and *Advanced Topics* chapters.

4. Added Revison History.

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                                             |

|-------------------------------------------------------------------------------|

| LIST OF TABLES                                                                |

| LIST OF FIGURES                                                               |

| Introduction                                                                  |

| 2 Simple Executive Configuration and APIs                                     |

| 2.1 Simple Executive Configuration                                            |

| 2.1.1 About FPA Pools                                                         |

| 2.2 Helper Functions                                                          |

| 2.3 PIP Functions                                                             |

| 2.4       PIP Data Structures and Defines       20                            |

| 2.4.1 The cvmx_pip_port_cfg_t Data Structure                                  |

| 2.4.2 The cvmx pip port tag cfg t Data Structure                              |

| 2.4.3 The cvmx pip parse mode t Defines (Parse Modes for Incoming Packets) 20 |

| 2.4.4 The cvmx pip tag mode t Defines (control the initial SSO Tag Value)     |

| 2.4.5 The cvmx pow tag type t Defines (control the initial SSO Tag Type)      |

| 2.4.6 The cvmx pip port status t Data Structure                               |

| 2.4.7 The cvmx pip err t Data Structure                                       |

| 2.4.8 The Packet Instruction Header Data Structure                            |

| 2.4.9 L1/L2 Receive Error Codes (WQE WORD2[RE] ==1)                           |

| 2.4.10 L3 (IP) Error Codes (WQE WORD2[IE]==1)                                 |

| 2.4.11 L4 Error Codes (WQE WORD2[LE]==1)                                      |

| 2.5 IPD Functions                                                             |

| 2.6 IPD Defines                                                               |

| 2.6.1 The cvmx ipd mode t Defines (How data is stored)                                                                                  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| 2.7 Beyond the SDK: Custom Software                                                                                                     |  |

| 3 IPD Input Ports                                                                                                                       |  |

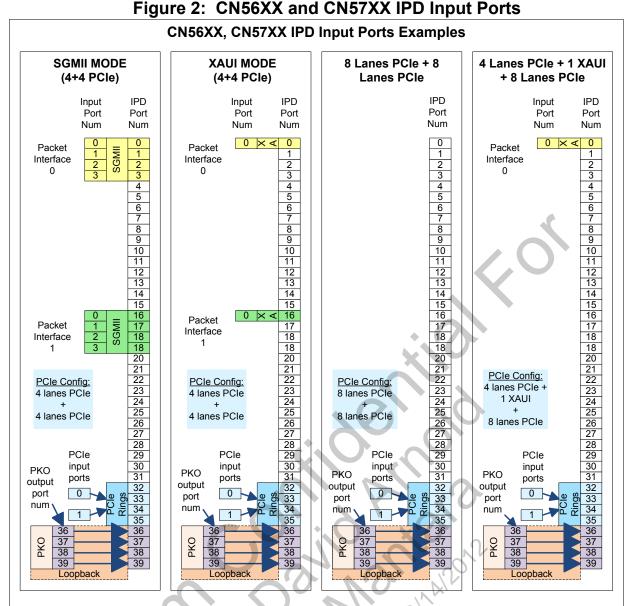

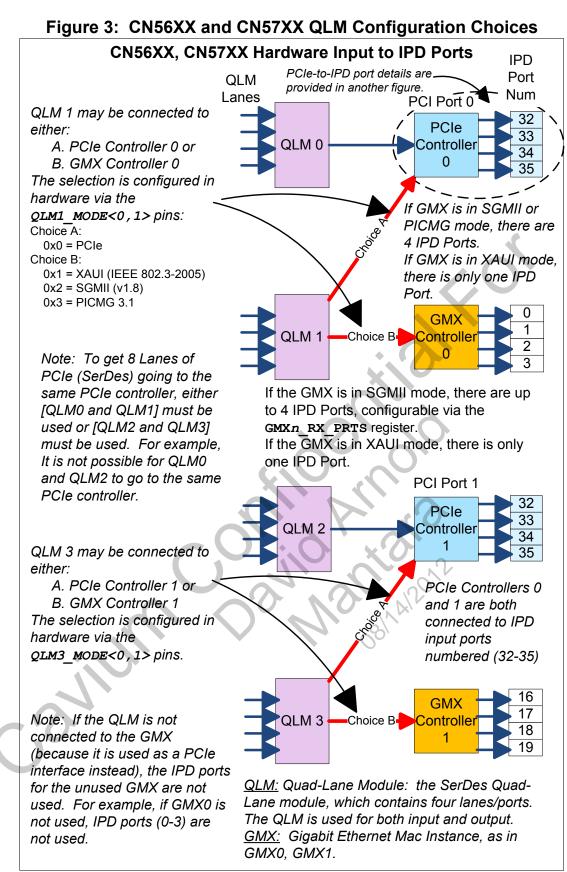

| 3.1 CN56XX and CN57XX IPD Input Ports                                                                                                   |  |

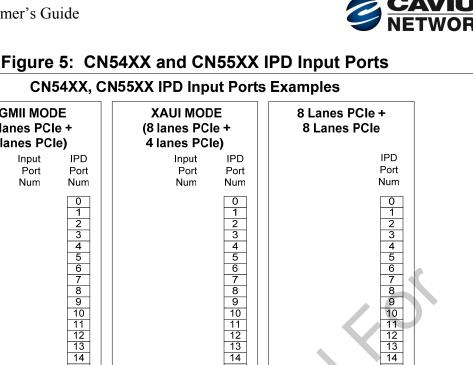

| 3.2 CN54XX and CN55XX IPD Input Ports                                                                                                   |  |

| 4 Incoming Packet Formats                                                                                                               |  |

| 4.1 Overall Processing Goal                                                                                                             |  |

| 4.2 Parsing Modes                                                                                                                       |  |

| 4.2.1 Optionally removing the CRC (FCS) (CRC stripping)                                                                                 |  |

| 4.3 Optional Packet Instruction Headers                                                                                                 |  |

| 4.3.1 The cvmx_pip_inst_hdr_t Data Structure                                                                                            |  |

| 4.3.2 RAW, RAWFULL, RAWSCH                                                                                                              |  |

| 4.4 Optional PCIe Instruction Headers                                                                                                   |  |

| 4.5 Registers to Configure Input Packet Format                                                                                          |  |

| 5 The Work Queue Entry Data Structure (WQE)                                                                                             |  |

| 5.1 Work Queue Entry Data Structure                                                                                                     |  |

| 5.2 Software WQE Data Structures                                                                                                        |  |

| 5.2.1 WQE The cvmx_wqe_t Data Structure                                                                                                 |  |

| 5.2.2 WQE WORD2: The cvmx pip wqe word2 Data Structure                                                                                  |  |

| 5.2.3 WQE WORD3: The cvmx buf ptr t data structure                                                                                      |  |

| 6 How Parse Mode Affects WQE WORD2 Data Structure                                                                                       |  |

| 6.1 All Parse Modes if L1/L2 Error Occurs                                                                                               |  |

| 6.2 Parse Mode = Skip-to-L2                                                                                                             |  |

| <ul> <li>6.1 All Parse Modes if L1/L2 Error Occurs</li> <li>6.2 Parse Mode = Skip-to-L2</li> <li>6.3 Parse Mode = Skip-to-IP</li> </ul> |  |

| 6.4 Parse Mode = Uninterpreted                                                                                                          |  |

| 6.5 Registers to Configure WOE WORD2 Content                                                                                            |  |

| <ul> <li>6.5 Registers to Configure WQE WORD2 Content</li> <li>6.6 Where to Find More Information About Parsing</li> </ul>              |  |

| 7 Scheduling (WQE WORD1)                                                                                                                |  |

| 7.1 Work Group Assignment (WQE WORD1 Group Field)                                                                                       |  |

| 7.1.1 Registers to Configure Group Assignment                                                                                           |  |

| 7.2       QoS Assignment                                                                                                                |  |

| 7.2.1 Registers to Configure OoS Assignment                                                                                             |  |

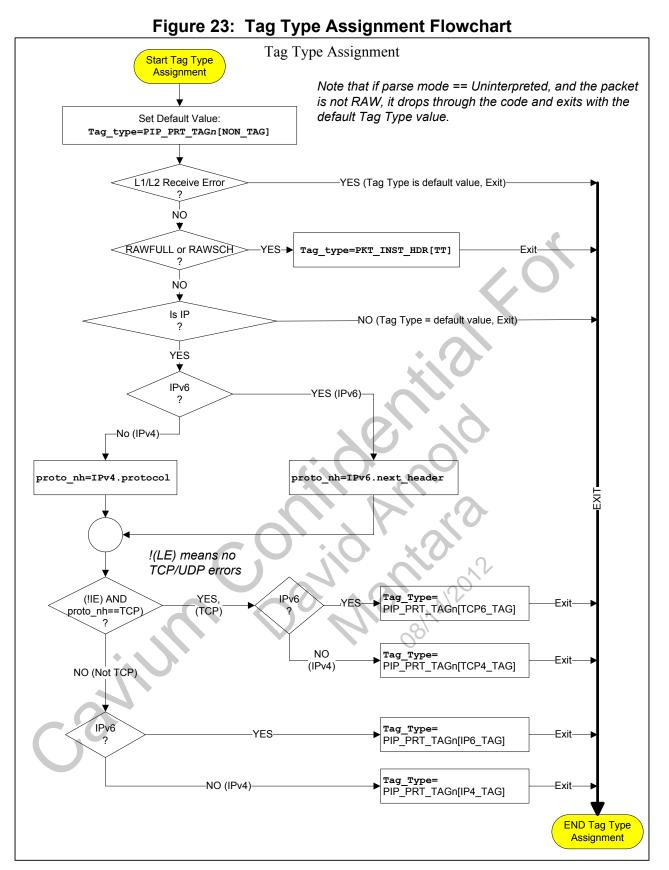

| 7.3 Tag Type Assignment                                                                                                                 |  |

| <ul><li>7.3 Tag Type Assignment.</li><li>7.3.1 WQE WORD1 Tag Type.</li></ul>                                                            |  |

| 7.3.2 Registers to Configure Tag Type Assignment                                                                                        |  |

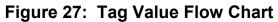

| 7.4 Tag Value Assignment                                                                                                                |  |

| 7.4.1 Registers to Configure Tag Value Assignment                                                                                       |  |

| 7.5 Using Watchers to Set QoS and Group                                                                                                 |  |

| 8 Security                                                                                                                              |  |

| 9 Error Check Configuration                                                                                                             |  |

| 9.1 CRC Check Configuration                                                                                                             |  |

| 10 Packet Storage                                                                                                                       |  |

| 10.1 The Part of the Received Data Which is Stored                                                                                      |  |

| 10.2 Packet Storage in Packet Data Buffers                                                                                              |  |

| 10.2.1 Storing WQE in Packet Data Buffer instead of WQE Buffer                                                                          |  |

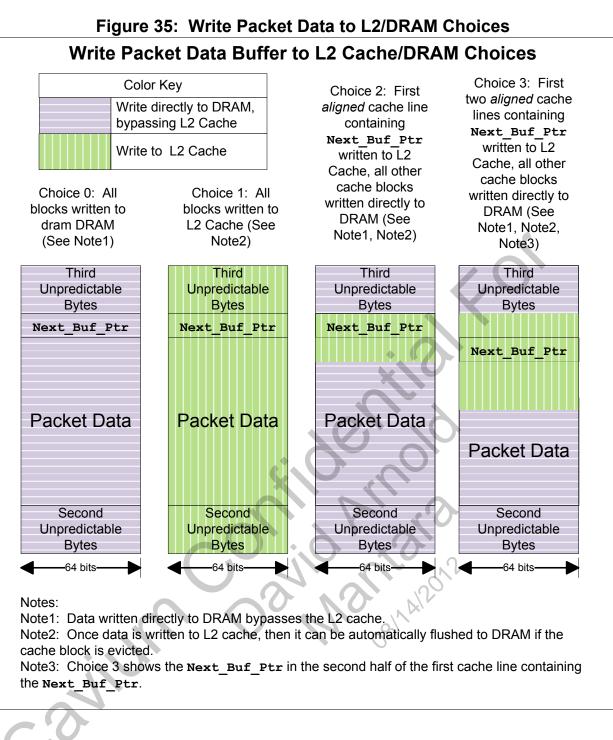

| 10.3 Choices for Writing Packet Data Buffer(s) to L2/DRAM                                                                               |  |

|                                                                                                                                         |  |

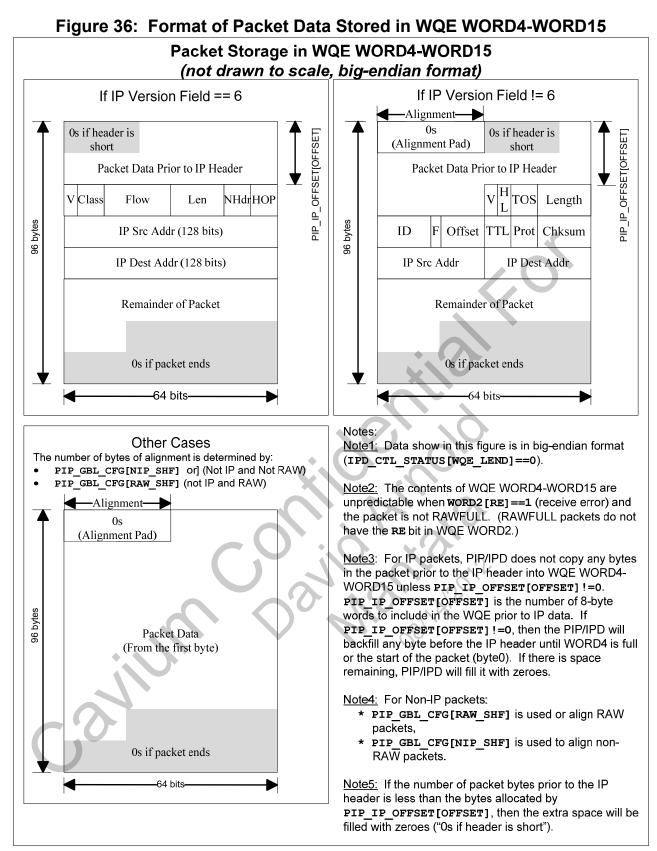

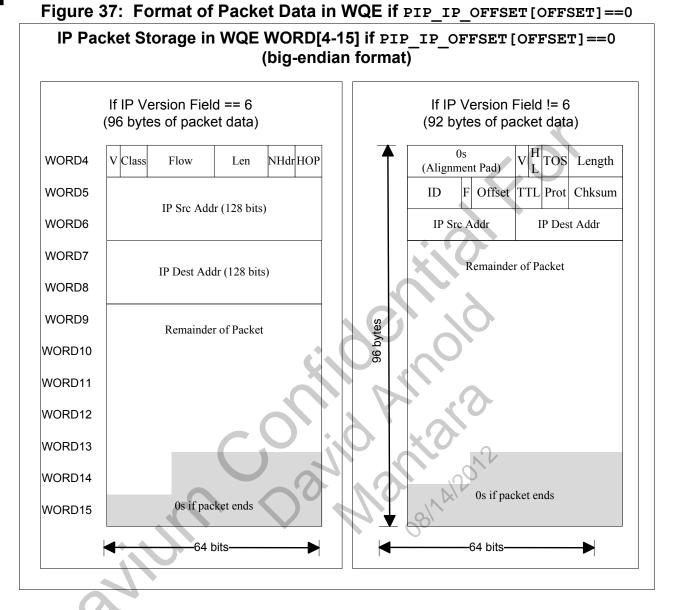

| 10.4 Packet Data Storage in WQE WORD4-15 1                                   | 10  |

|------------------------------------------------------------------------------|-----|

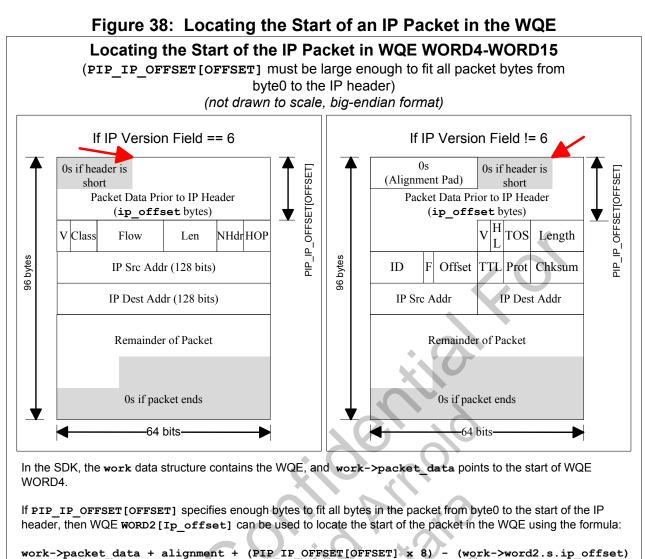

| 10.4.1 Finding the Start of an IP Packet in the WQE 1                        | 13  |

| 10.4.2 Dynamic Short Storage in WQE1                                         |     |

| 10.5 Accessing Packet Data When Some Packets are Dynamic Shorts              | 15  |

| 10.6 Configuring Packet Storage                                              |     |

| 11 Statistics (Performance, Debugging)1                                      | 21  |

| 12 Congestion Control (Backpressure, Packet Drop, RED, WRED)1                | 23  |

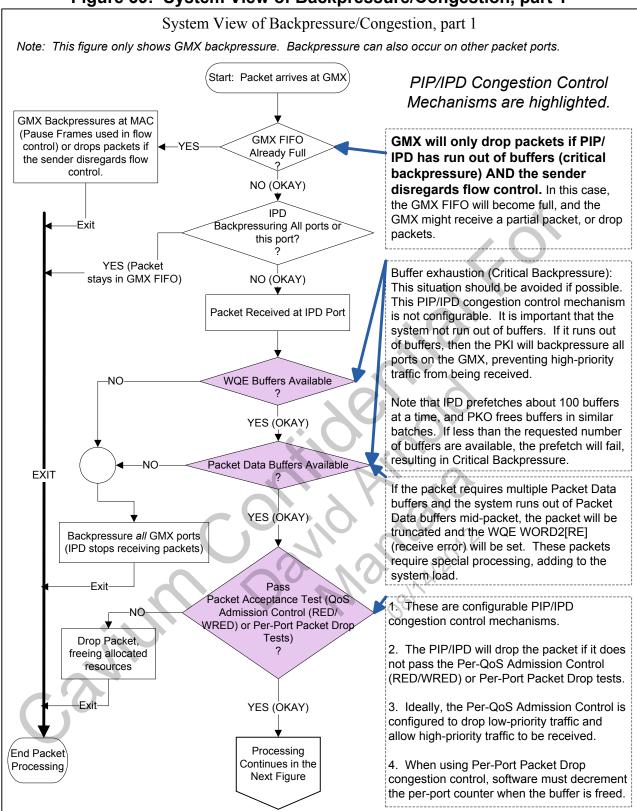

| 12.1 System-Level View of Congestion: Causes and Prevention                  | 23  |

| 12.1.1 Congestion Management Design Issues:                                  | 23  |

| 12.1.2 Normal Congestion                                                     |     |

| 12.1.3 Unexpected Congestion                                                 | 24  |

| 12.2 Overview of Congestion-Control Mechanisms Provided by PIP/IPD 1         | 27  |

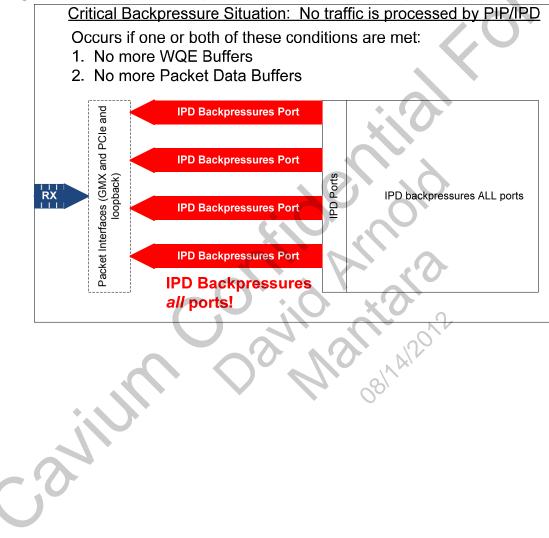

| 12.3 Critical Backpressure (Buffer Exhaustion)                               | 28  |

| 12.4 PIP/IPD Congestion-Control Configuration                                | 29  |

| 12.4.1 Basic QoS RED Configuration: cvmx_helper_setup_red()1                 | 30  |

| 12.4.2 Basic QoS WRED Configuration: cvmx_helper_setup_red_queue() 1         | 30  |

| 12.4.3 Custom Configuration                                                  |     |

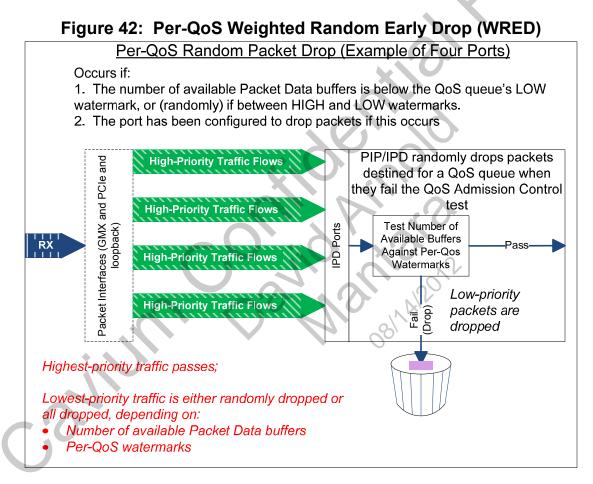

| 12.5 Per-QoS Admission Control (RED and WRED) (PQ-RED) 1                     | 30  |

| 12.5.1 The Simplest Case: Snapshot Value (Recommended) 1                     | 34  |

| 12.5.2 More Complex: Moving Average                                          | 37  |

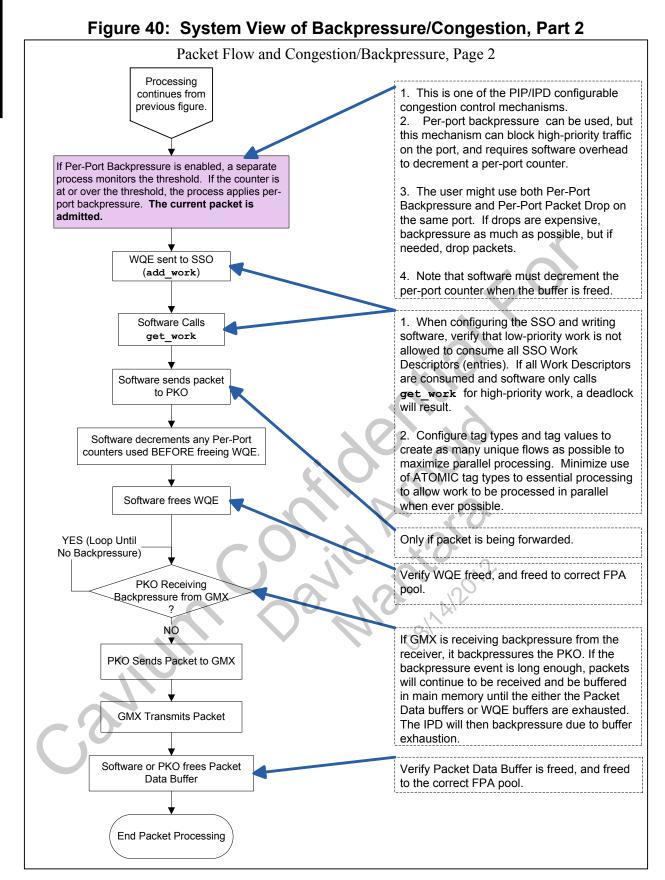

| 12.6 Per-Port Congestion Control (Backpressure, Packet Drop) (PP-B, PP-PD) 1 | 39  |

| 12.6.1 Per-Port Backpressure (PP-B)                                          | 40  |

| 12.6.1Per-Port Backpressure (PP-B)112.6.2Per-Port Packet Drop (PP-PD)1       | 44  |

| 12.7 Per-Port RED                                                            | 49  |

| 13 Per QoS/Port Buffer Tracking                                              | 149 |

| 14 Appendix A: PIP/IPD Registers and Register Fields                         | 49  |

| 15 Appendix B: Industry-Standard Reference Information                       | 50  |

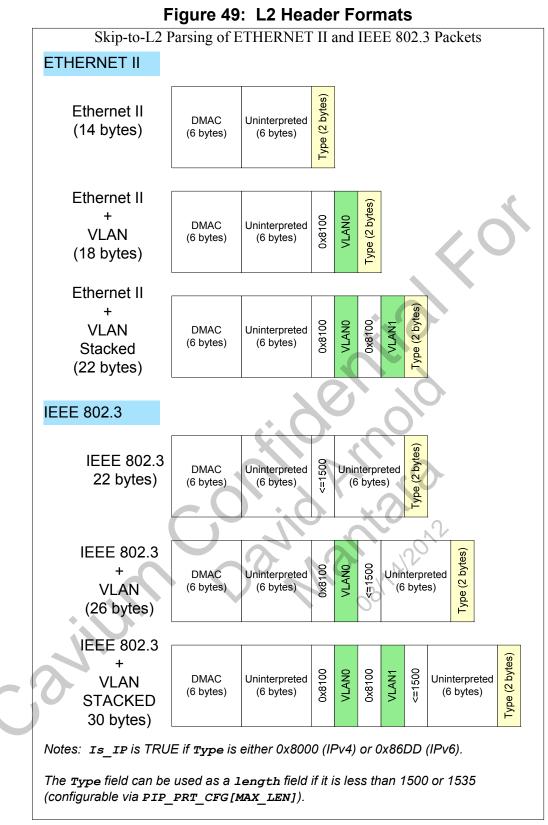

| 15.1 L2 Header Formats                                                       | 51  |

| 15.1.1 L2 Header Type Field Values (EtherType)1                              |     |

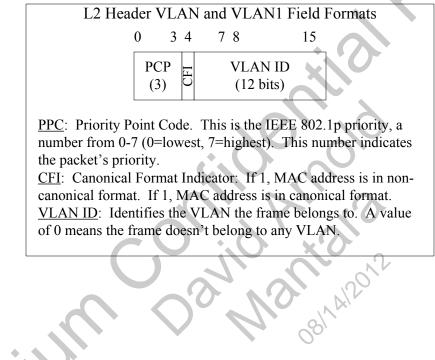

| 15.1.2 L2 Header VLAN, VLAN 1 Field Details                                  | 52  |

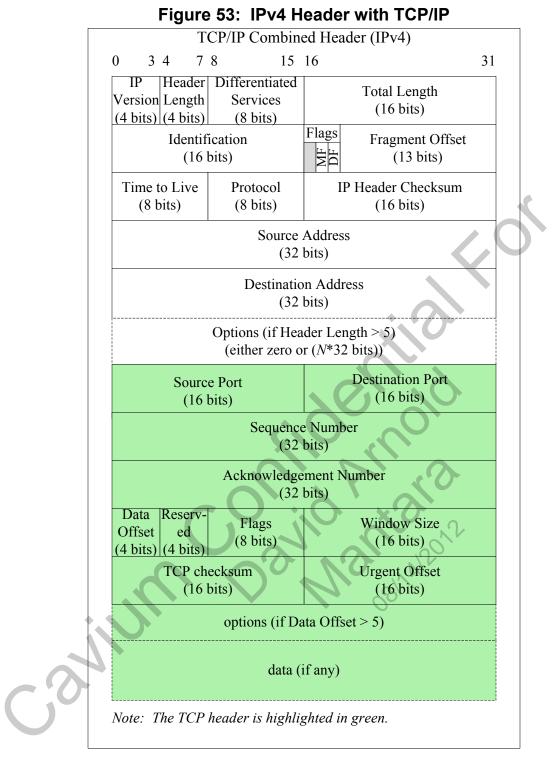

| 15.2       L3: IPv4 Header                                                   | 53  |

| 15.2.1 IPv4 Protocol Field Values                                            | 55  |

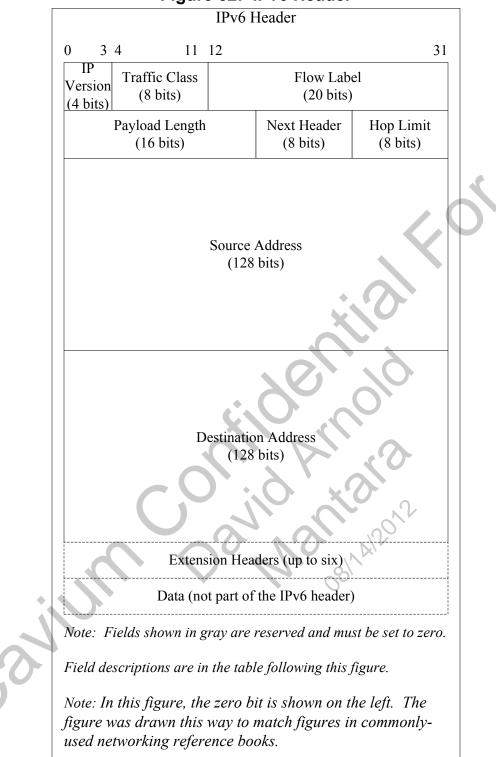

| 15.3 L3: IPv6 Header                                                         | 56  |

| 15.3       L3: IPv6 Header                                                   | 58  |

| 15.5 L4: UDP Header 1                                                        | 59  |

| 16 Appendix C: Input Packet Parsing Details                                  | 60  |

| 17 Appendix D: A Note about Configuring GMX Backpressure                     | 63  |

| 18 Appendix E: Example Code (linux-filter)1                                  | 64  |

| 19 Appendix F: Input Port Configuration                                      | 68  |

| 19.1 Fast Links for Input Port Figures1                                      | 81  |

# LIST OF TABLES

| Table 1: Summary of Relevant Functions    11                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2: Simple Executive PIP/IPD Configuration Variables.    13                                                                                                     |

| Table 3: Default FPA Pool Configuration   15                                                                                                                         |

| Table 4: Packet Data Buffers Information   15                                                                                                                        |

| Table 5: Work Queue Entry Buffers Information                                                                                                                        |

| Table 6: Helper Functions       17                                                                                                                                   |

| Table 7: PIP Functions       19                                                                                                                                      |

| Table 8: IPD API Functions   25                                                                                                                                      |

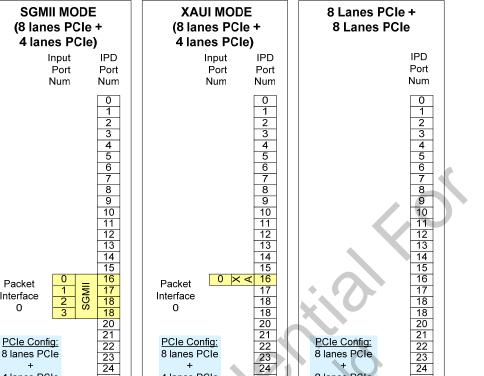

| Table 9: CN56XX and CN57XX Packet Input Configuration Options       28                                                                                               |

| Table 10: CN54XX and CN55XX Packet Input Configuration Options       34                                                                                              |

| Table 11: Registers to Configure Input Packet Format                                                                                                                 |

| Table 11: Registers to Configure Input Packet Format       48         Table 12: Registers to Configure Work Queue Entry Details       49                             |

| Table 12: Registers to compare work Queue Entry Details         Table 13: Fields: WQE WORD2 Fields if L1/L2 Error (CASE 3C)                                          |

| Table 14: WQE WORD2 Fields for Skip-to-L2 and Is_IP (CASE 2A)                                                                                                        |

| Table 14: WQE WORD2 Fields for Skip-to-L2 and IS_IT (CASE 2A)                                                                                                        |

| Table 15: WQE WORD2 Fields for Skip-to-L2 and NOT IF (CASE SA)       02         Table 16: WQE WORD2 Fields for Skip-to-IP (CASE 2B)       64                         |

| Table 10: WQE WORD2 Fields for SKIP-to-II (CASE 2B)       64         Table 17: WQE WORD2 Fields for RAWFULL (CASE 1A and CASE 1B)       68                           |

|                                                                                                                                                                      |

| Table 18: WQE WORD2 Fields for Uninterpreted and not RAW (CASE 3B)       69         Table 10: Pagisters to Configure Work Output Entry WORD2       71                |

| Table 19: Registers to Configure Work Queue Entry WORD2       71         Table 20: Registers to Configure WOE WORD1 Crown Assisters and Configure WOE WORD2       75 |

| Table 20: Registers to Configure WQE WORD1 Group Assignment       75         Table 21: Registers to Configure WQE WORD1 QoS Assignment       70                      |

| Table 21: Registers to Configure WQE WORD1 QoS Assignment       79         Table 22: Desisters to Configure WQE WORD1 To Table Assignment       82                   |

| Table 22: Registers to Configure WQE WORD1 Tag Type Assignment    83      Table 22: Registers to Configure WQE WORD1 Tag Type Assignment    83                       |

| Table 23: Registers to Configure WQE WORD1 Tag Value Assignment                                                                                                      |

| Table 24: Registers to Configure Watchers                                                                                                                            |

| Table 25: Registers to Configure IP Security                                                                                                                         |

| 1 able 26: Registers 10 Configure Error Checking                                                                                                                     |

| Table 27: Registers Used to Configure CRC Check   102                                                                                                                |

| Table 28: Packet Data Buffer Write to L2/DRAM Choices (Global Option)       109                                                                                      |

| Table 29: Registers to Configure Packet Storage117Table 30: Statistics Register Fields (Read Only)122                                                                |

|                                                                                                                                                                      |

| Table 31: Overview of PIP/IPD Congestion Control Mechanisms    127                                                                                                   |

| Table 32: Critical Backpressure Overview                                                                                                                             |

| Table 33: Overview of Per-QoS RED and WRED                                                                                                                           |

| Table 34: Registers to Configure Per-QoS RED/WRED – Snapshot                                                                                                         |

| Table 35: Registers to Configure Per-QoS RED/WRED – Moving Average                                                                                                   |

| Table 36: Per-Port Backpressure Overview    142                                                                                                                      |

| Table 37: Registers to Configure Per-Port Backpressure    142                                                                                                        |

| Table 38:    Per-Port Packet Drop Overview    146                                                                                                                    |

| Table 39: Registers to Configure Per-Port Packet Drop                                                                                                                |

| Table 40:    L2 Header Type Field Values (EtherType)                                                                                                                 |

| Table 41: IPv4 Header Fields    153                                                                                                                                  |

| Table 42: IPv4 Protocols   155                                                                                                                                       |

| Table 43: IPv6 Header Fields    157                                                                                                                                  |

| Table 44: Overview of GMX Registers Used to Configure Backpressure                                                                                                   |

# **LIST OF FIGURES**

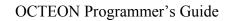

| Figure 1: Overview of PIP/IPD Processing                                                                     | 10       |

|--------------------------------------------------------------------------------------------------------------|----------|

| Figure 2: CN56XX and CN57XX IPD Input Ports                                                                  | 29       |

| Figure 3: CN56XX and CN57XX QLM Configuration Choices                                                        | 31       |

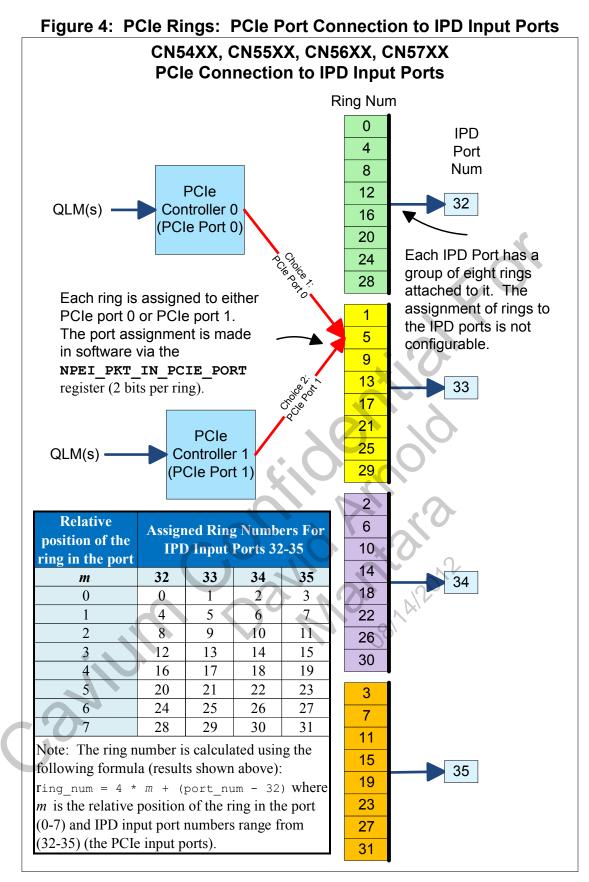

| Figure 4: PCIe Rings: PCIe Port Connection to IPD Input Ports                                                |          |

| Figure 5: CN54XX and CN55XX IPD Input Ports                                                                  |          |

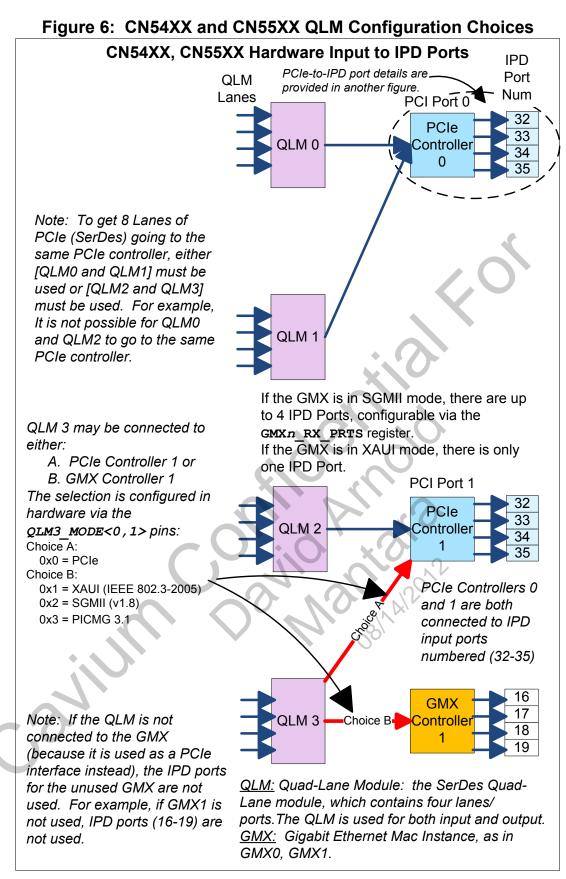

| Figure 6: CN54XX and CN55XX QLM Configuration Choices                                                        |          |

| Figure 7: Parsing Mode Choices Without Packet Instruction Header                                             |          |

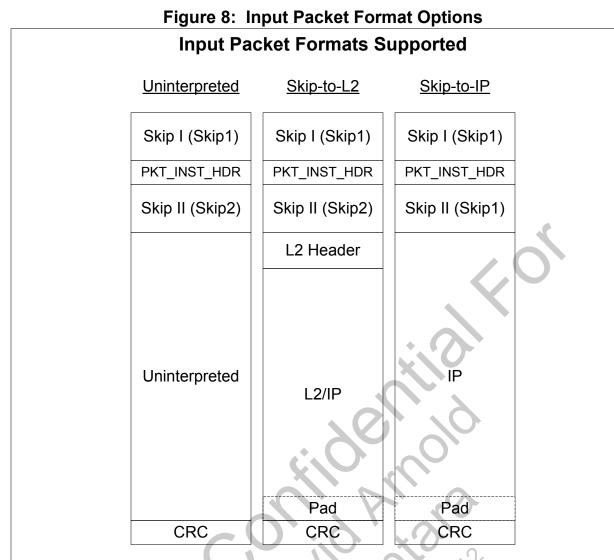

| Figure 8: Input Packet Format Options                                                                        |          |

| Figure 9: Packet Instruction Header – Hardware View                                                          |          |

| Figure 10: WQE Information Copied From the Packet Instruction Header                                         |          |

| Figure 11: PCIe Instruction Header Conversion to Packet Instruction Header                                   |          |

| Figure 12: Work Queue Entry Data Structure – Hardware View                                                   |          |

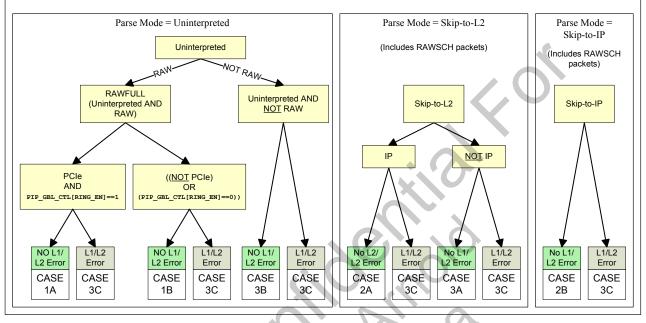

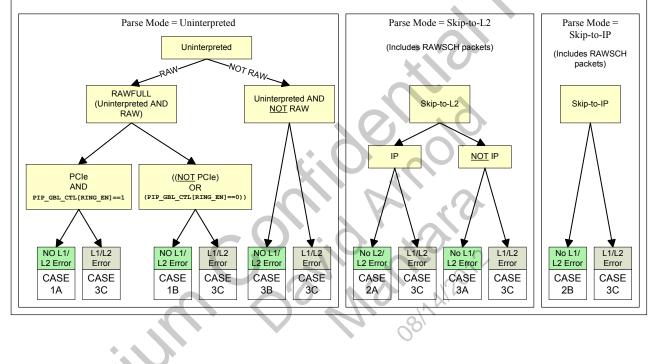

| Figure 13: Parsing Cases                                                                                     |          |

| Figure 14: WORD2 if L1/L2 Error (CASE 3C)                                                                    |          |

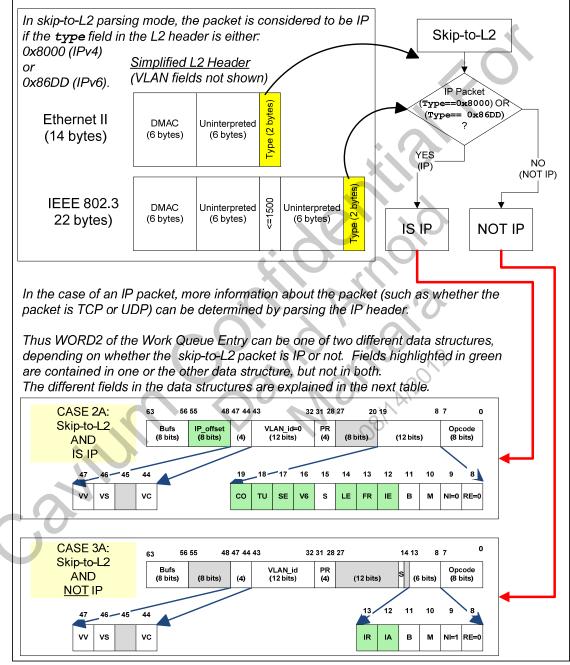

| Figure 15: WORD2 if PM=Skip-to-L2, No L1/L2 Errors (CASE 2A, CASE 3A)                                        |          |

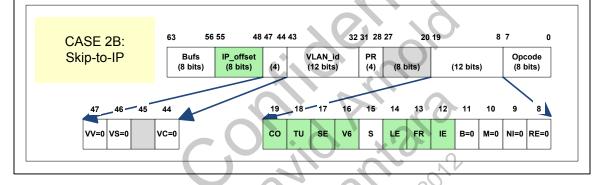

| Figure 16: WORD2 if PM=Skip-to-IP and No L1/L2 Errors (CASE 2B)                                              |          |

| Figure 17: WORD2 if PM=Unint., RAW, No L1/L2 Errors (CASE 1A, CASE 1B)                                       |          |

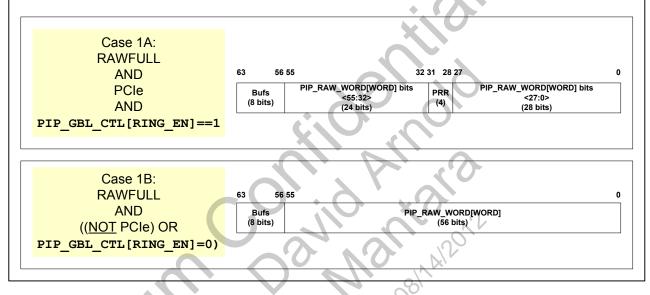

| Figure 18: WORD2 if PM=Unint., NOT RAW, No L1/L2 Errors (CASE 3B)                                            |          |

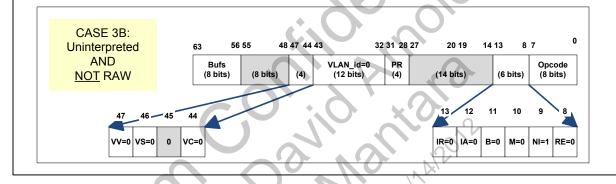

|                                                                                                              |          |

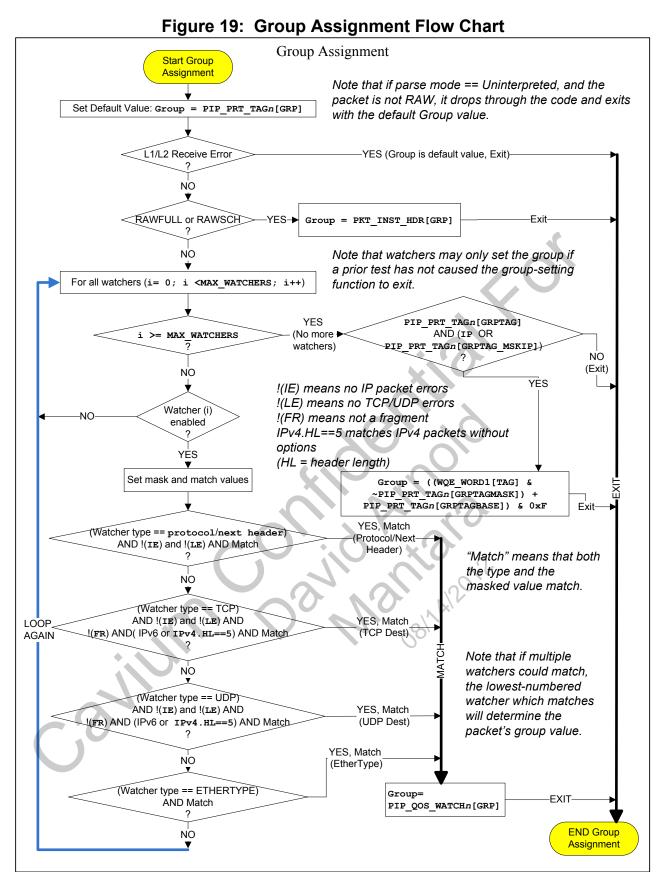

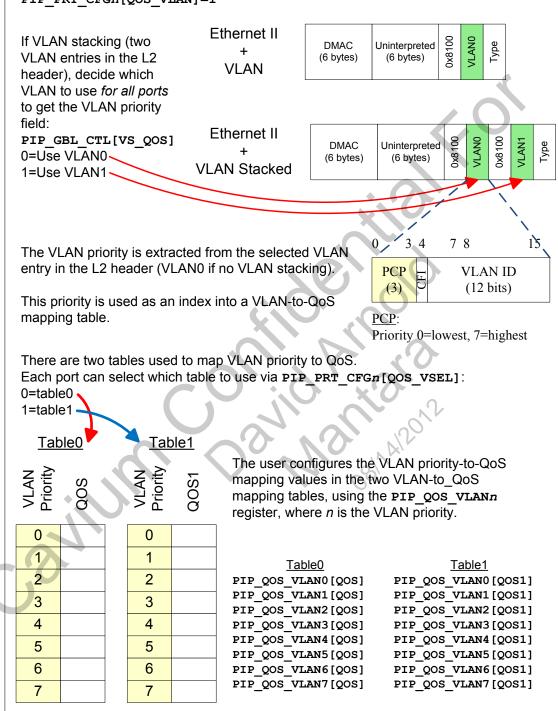

| Figure 19: Group Assignment Flow Chart<br>Figure 20: Deriving QoS From VLAN Priority                         | 76       |

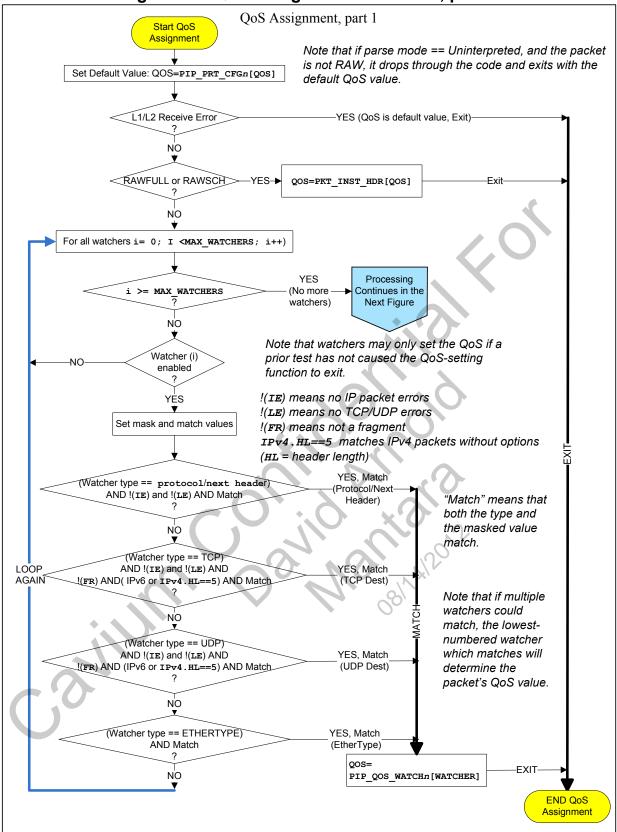

| Figure 21: OoS Assignment Flowchart, part 1                                                                  | 77       |

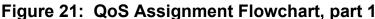

| Figure 22: OoS Assignment Flowchart, part 2                                                                  | 78       |

| Figure 23: Tag Type Assignment Flowchart                                                                     |          |

| Figure 24: Tag Value Data Structure                                                                          | 84       |

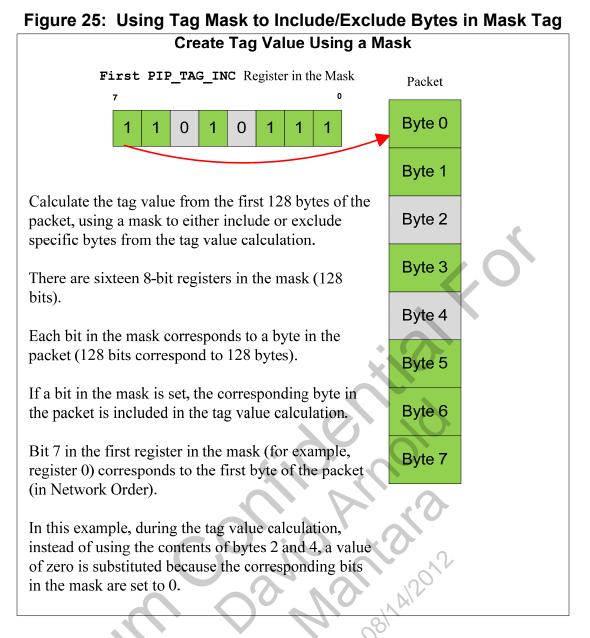

| Figure 25: Using Tag Mask to Include/Exclude Bytes in Mask Tag                                               | 85       |

| Figure 26: Tag Mask Register Bits Correspondence to Packet Data Bytes                                        |          |

| Figure 27: Tag Value Flow Chart                                                                              | 88       |

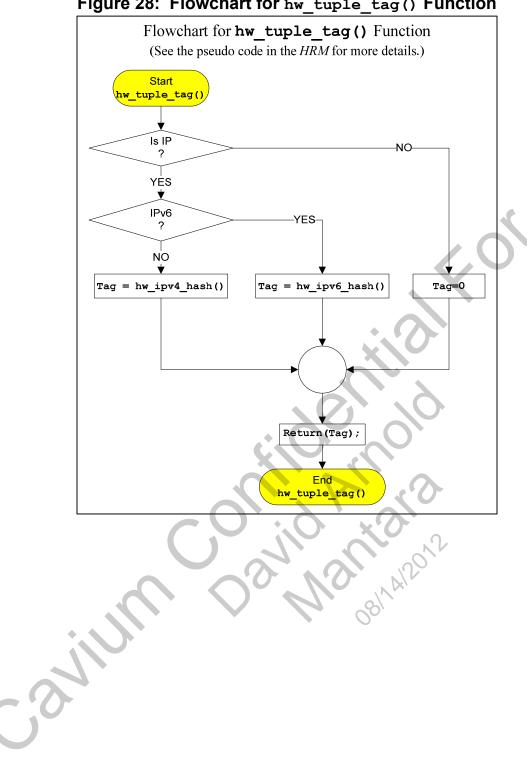

| Figure 28: Flowchart for hw tuple tag() Function                                                             | 89       |

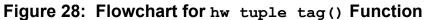

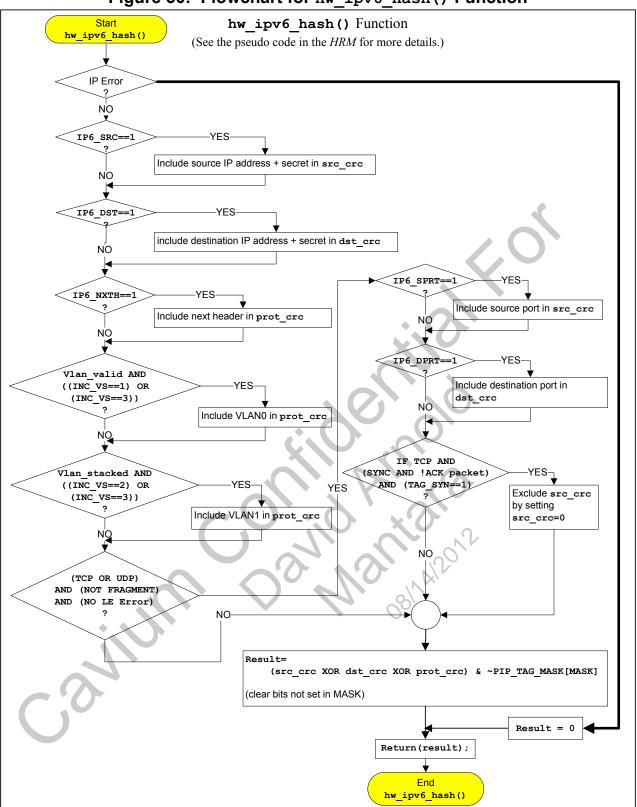

| Figure 29: Flowchart for hw_ipv4_hash() Function<br>Figure 30: Flowchart for hw_ipv6_hash() Function         | 90       |

| Figure 30: Flowchart for hw_ipv6_hash() Function                                                             | 91       |

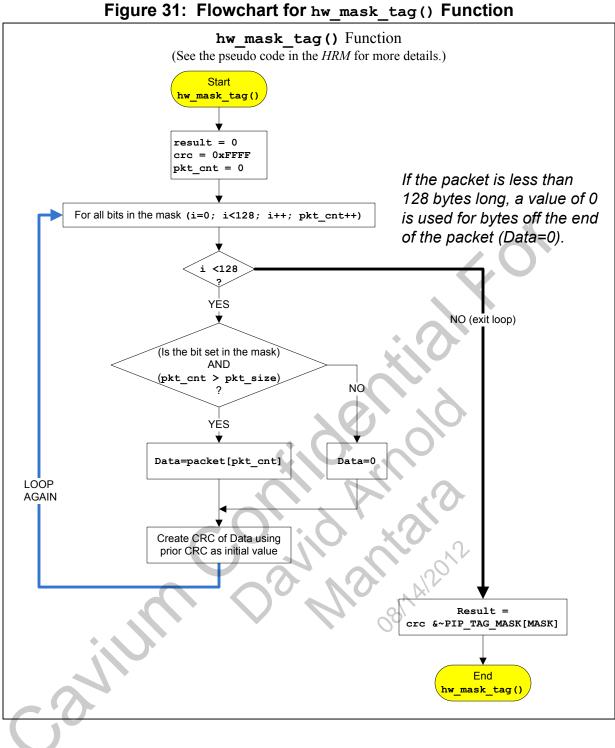

| Figure 31: Flowchart for hw mask tag() Function                                                              | 91<br>92 |

|                                                                                                              |          |

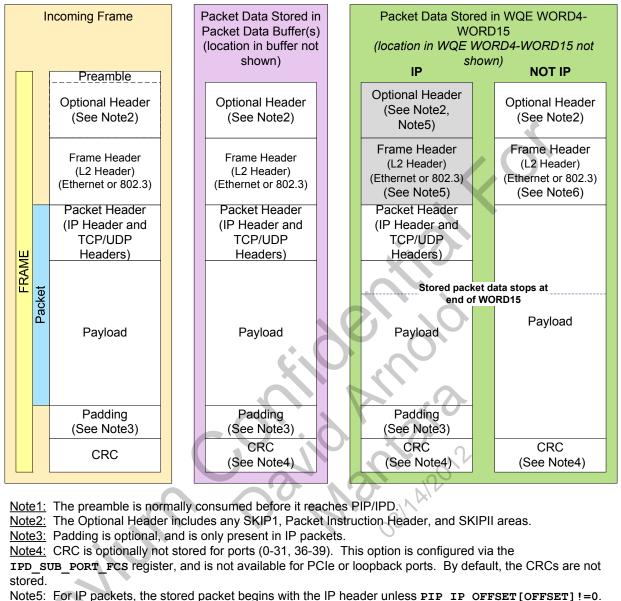

| Figure 32: Overview of Storing Received Data<br>Figure 33: Next Buffer Pointer (Next Buf Ptr) Data Structure | 104      |

| Figure 33: Next Burler Foliner (Next_Burl_FCF) Data Structure                                                |          |

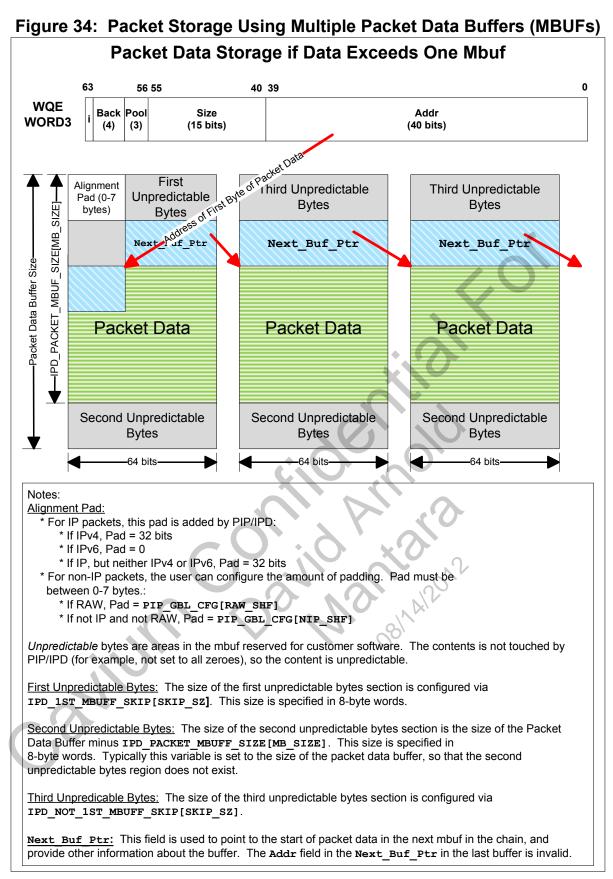

| Figure 34. Facket Storage Osing Multiple Facket Data Burlets (MBOFS)                                         |          |

| Figure 36: Format of Packet Data Stored in WQE WORD4-WORD15                                                  | 110      |

|                                                                                                              |          |

| Figure 37: Format of Packet Data in WQE if PIP_IP_OFFSET[OFFSET] == 0                                        |          |

| Figure 38: Locating the Start of an IP Packet in the WQE                                                     |          |

| Figure 39: System View of Backpressure/Congestion, part 1                                                    |          |

| Figure 40: System View of Backpressure/Congestion, Part 2                                                    |          |

| Figure 41: Critical Backpressure Situation, Backpressure on All Ports                                        |          |

| Figure 42: Per-QoS Weighted Random Early Drop (WRED)                                                         |          |

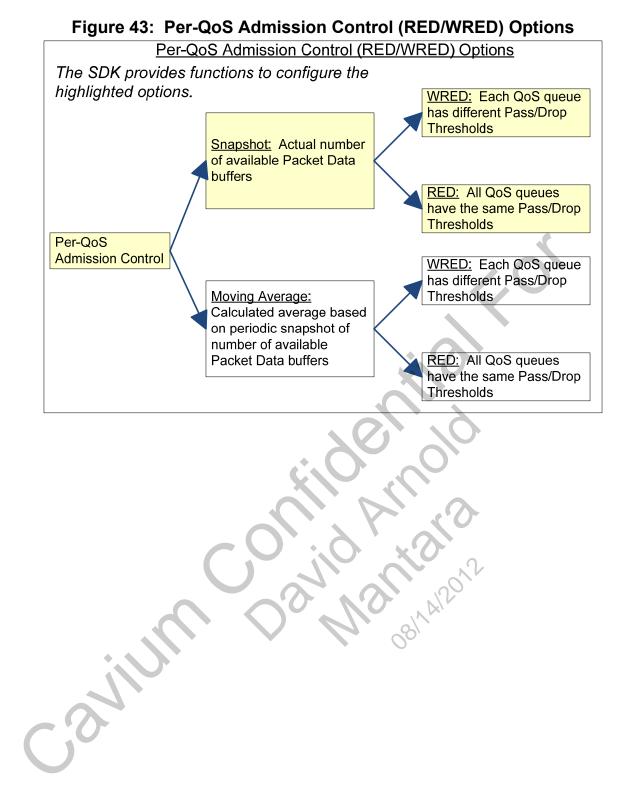

| Figure 43: Per-QoS Admission Control (RED/WRED) Options                                                      | 133      |

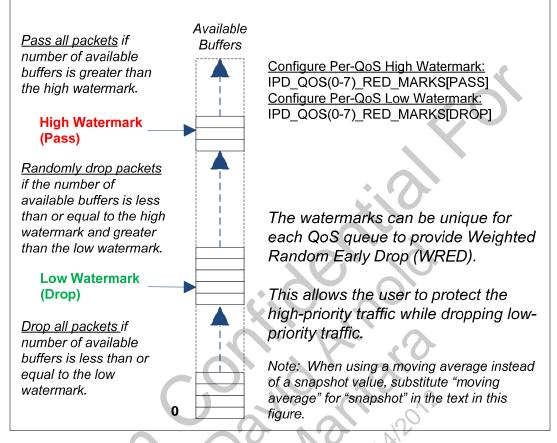

| Figure 44: | Per-QoS RED – Using Snapshot Value                        | 134 |  |

|------------|-----------------------------------------------------------|-----|--|

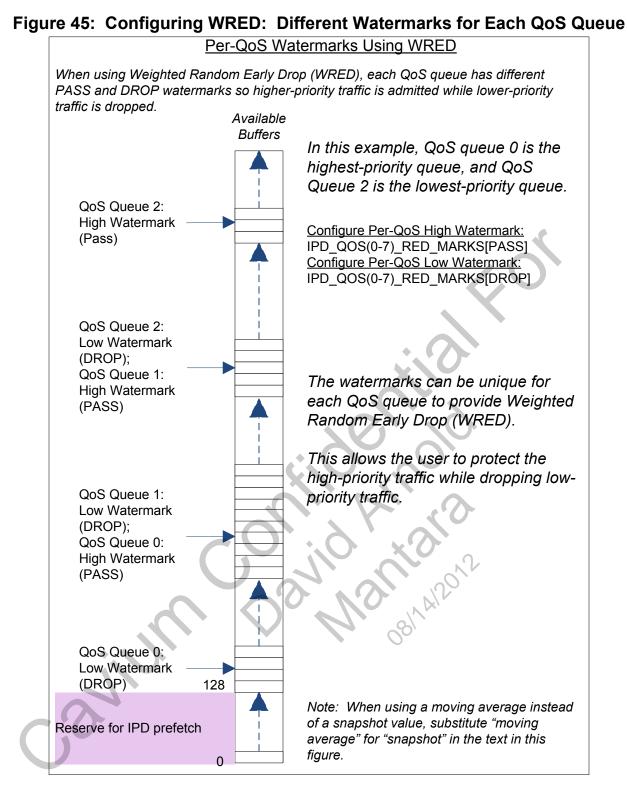

|            | Configuring WRED: Different Watermarks for Each QoS Queue |     |  |

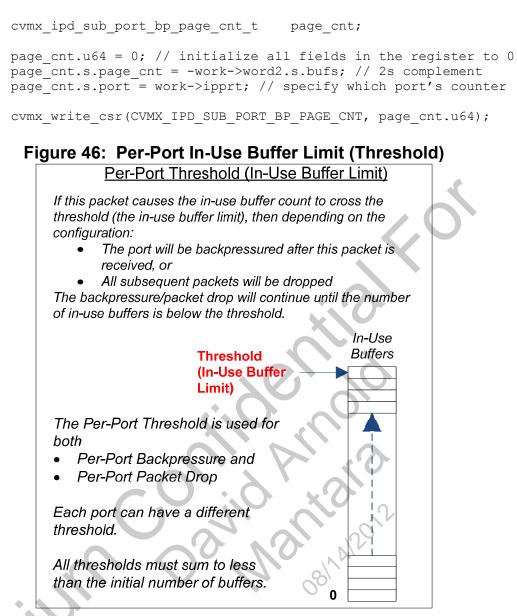

|            | 46: Per-Port In-Use Buffer Limit (Threshold)              |     |  |

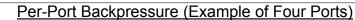

| Figure 47: | Congestion Control: Per-Port Backpressure                 | 141 |  |

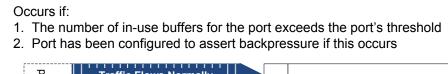

|            | Congestion Control: Per-Port Packet Drop                  |     |  |

|            | L2 Header Formats                                         |     |  |

| •          | L2 Header and VLAN, VLAN1 Field Details – CFI, VLAN ID    |     |  |

| •          | IPv4 Header                                               |     |  |

| Figure 52: | IPv6 Header                                               | 156 |  |

|            | IPv4 Header with TCP/IP                                   |     |  |

| Figure 54: | UDP Header                                                | 159 |  |

| •          | Input Packet Parsing Cases                                |     |  |

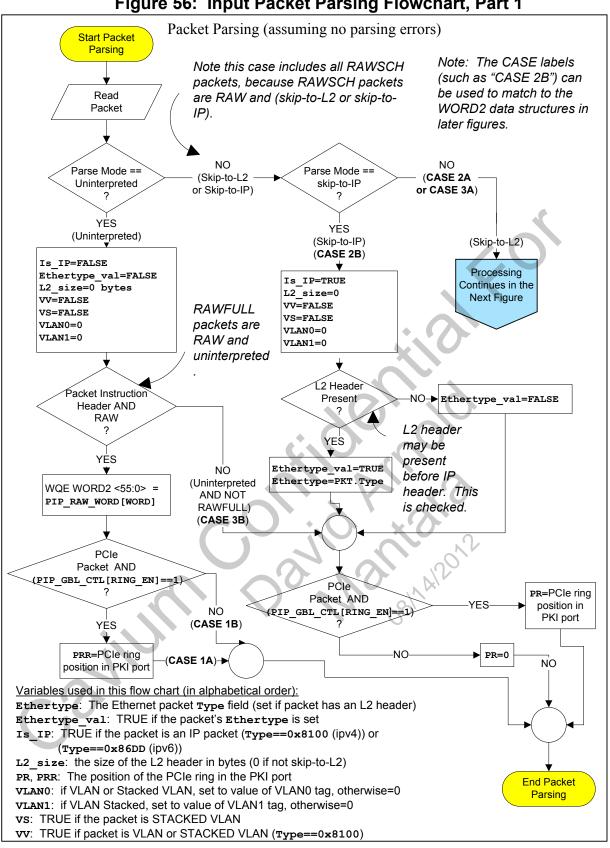

|            | Input Packet Parsing Flowchart, Part 1                    |     |  |

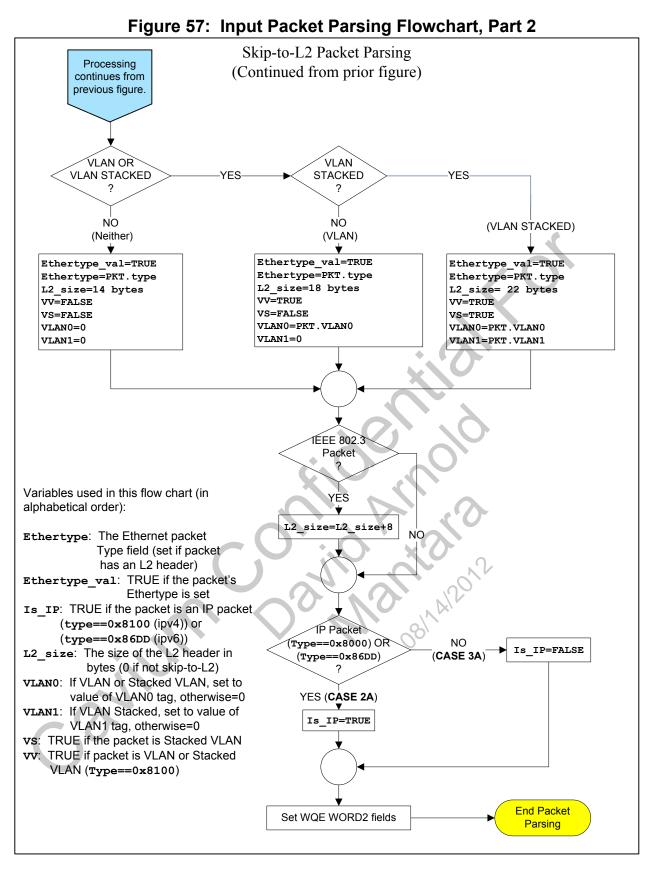

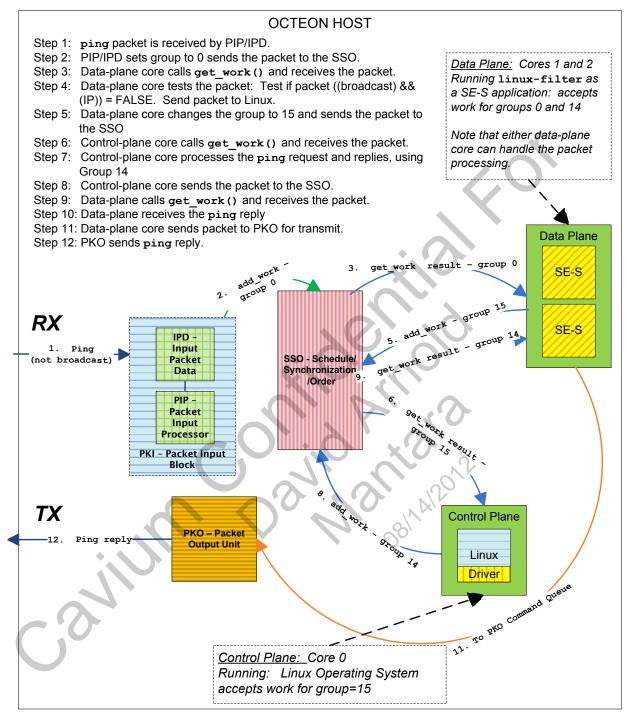

| Figure 57: | Input Packet Parsing Flowchart, Part 2                    | 162 |  |

| Figure 58: | Linux-Filter                                              | 165 |  |

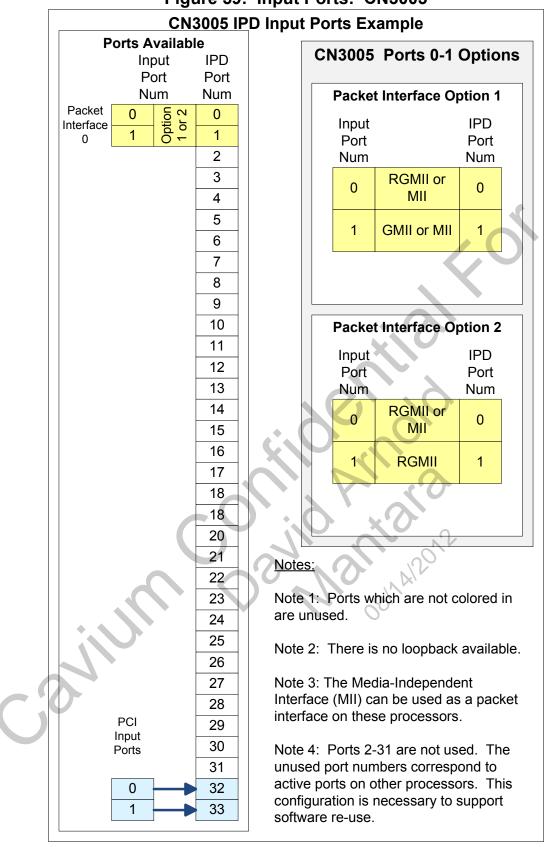

| Figure 59: | Input Ports: CN3005                                       | 169 |  |

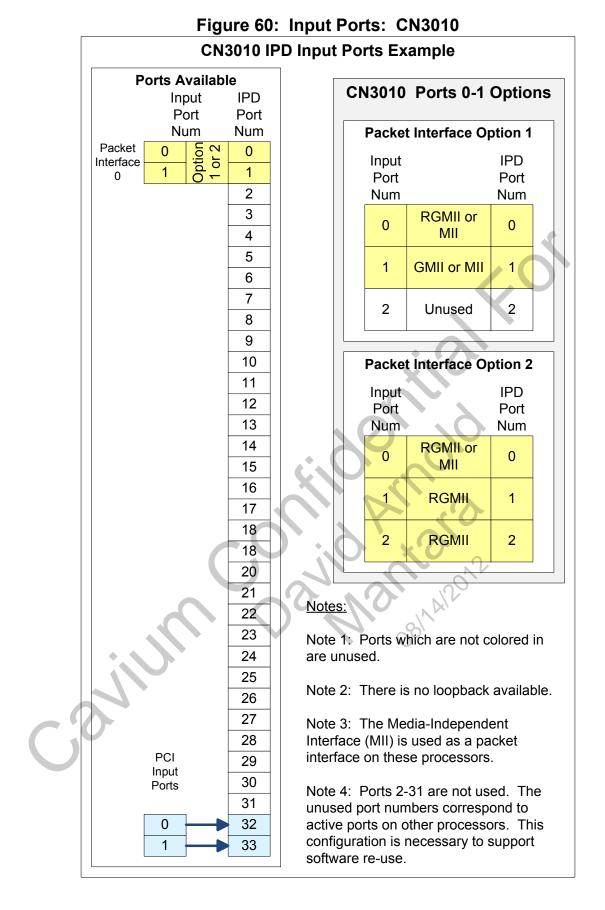

|            | Input Ports: CN3010                                       |     |  |

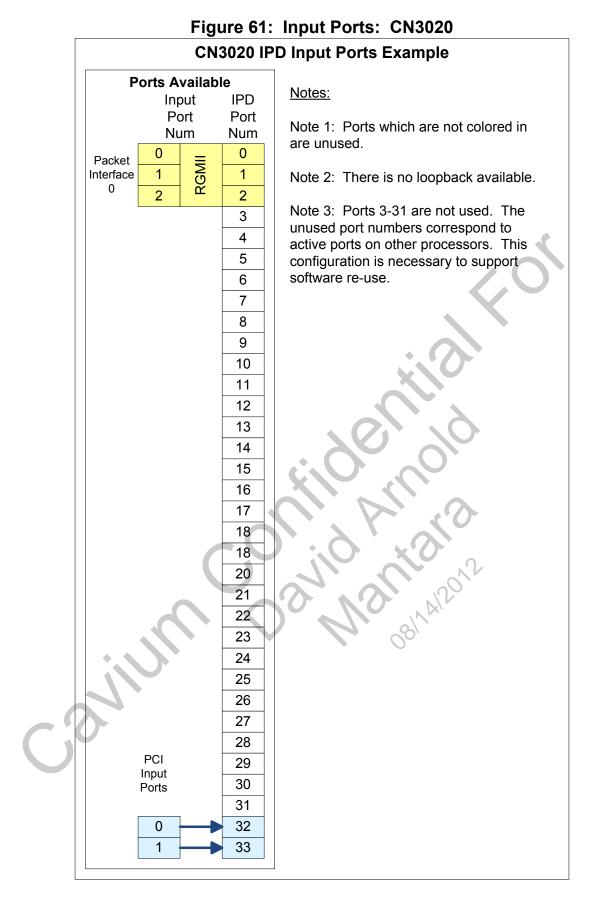

| Figure 61: | Input Ports: CN3020                                       | 171 |  |

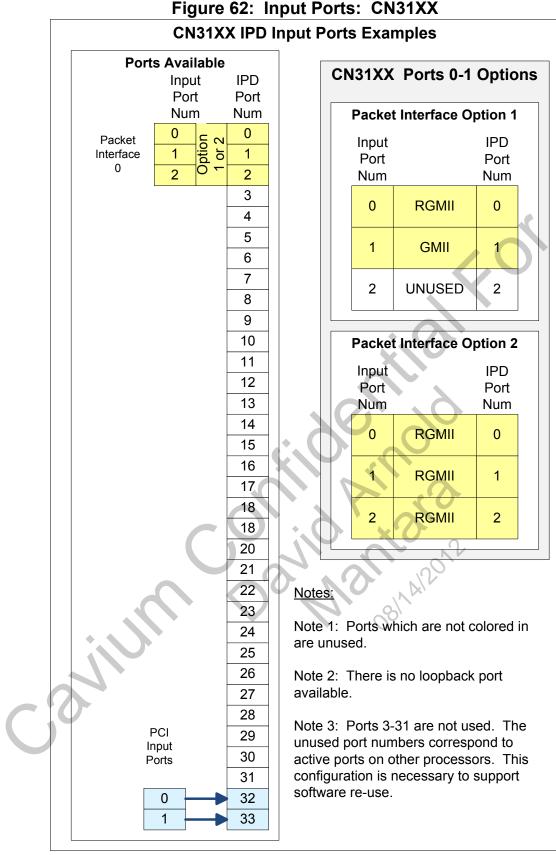

| Figure 62: | Input Ports: CN3020<br>Input Ports: CN31XX                | 172 |  |

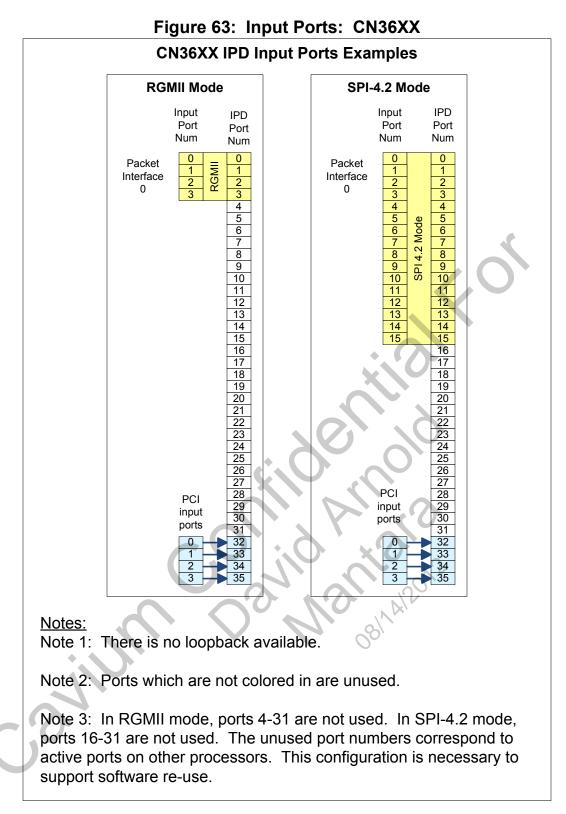

| Figure 63: | Input Ports: CN36XX                                       | 173 |  |

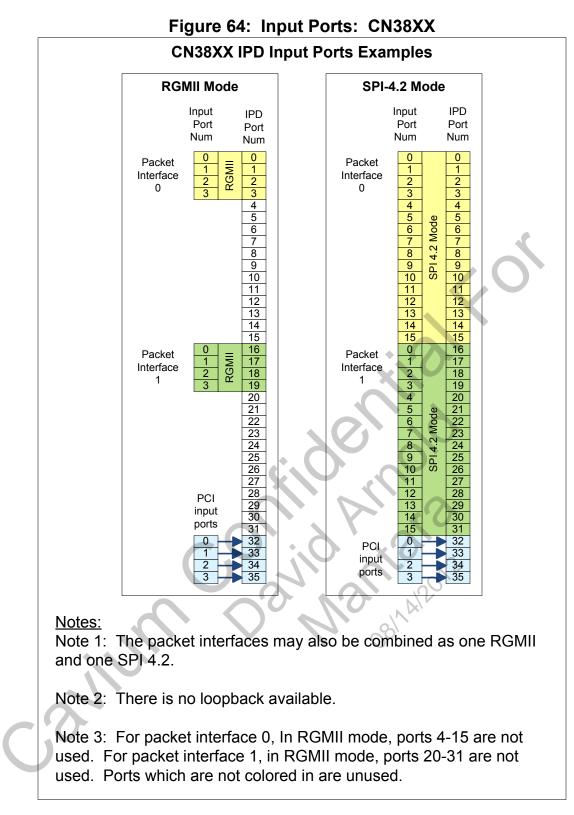

| Figure 64  | Input Ports: CN38XX                                       | 174 |  |

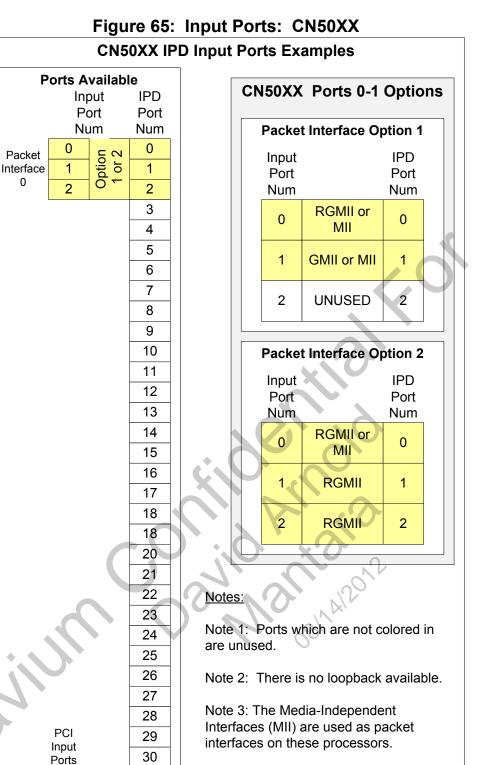

| Figure 65: | Input Ports: CN50XX<br>Input Ports: CN52XX                | 175 |  |

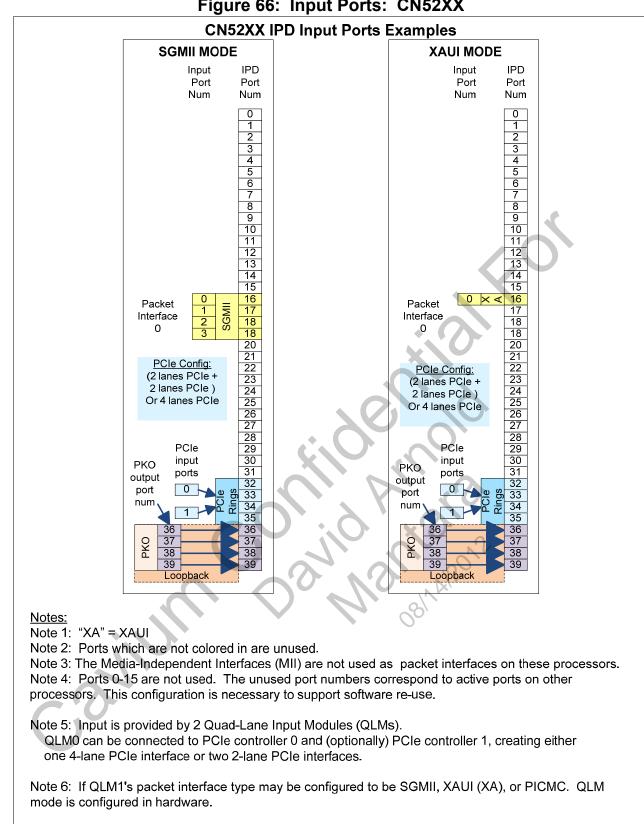

| Figure 66: | Input Ports: CN52XX                                       | 176 |  |

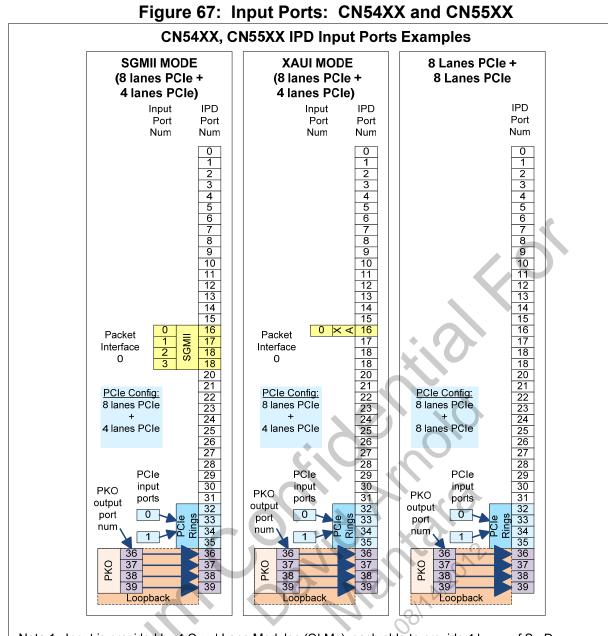

| Figure 67: | Input Ports: CN54XX and CN55XX                            | 177 |  |

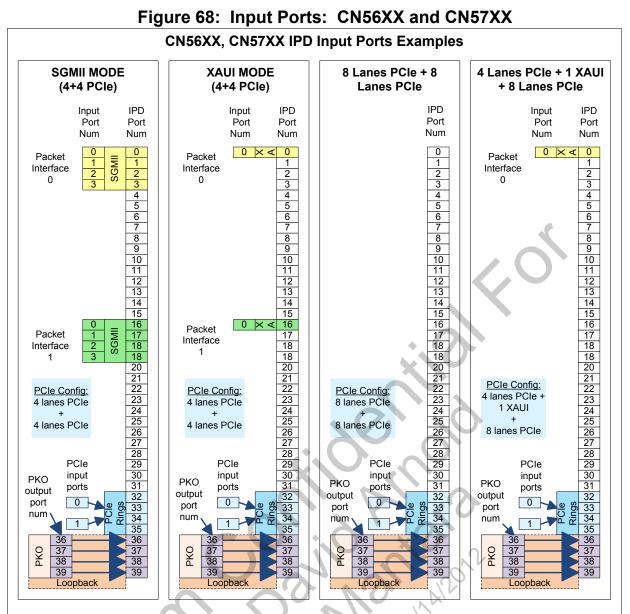

| Figure 68: | Input Ports: CN56XX and CN57XX                            | 178 |  |

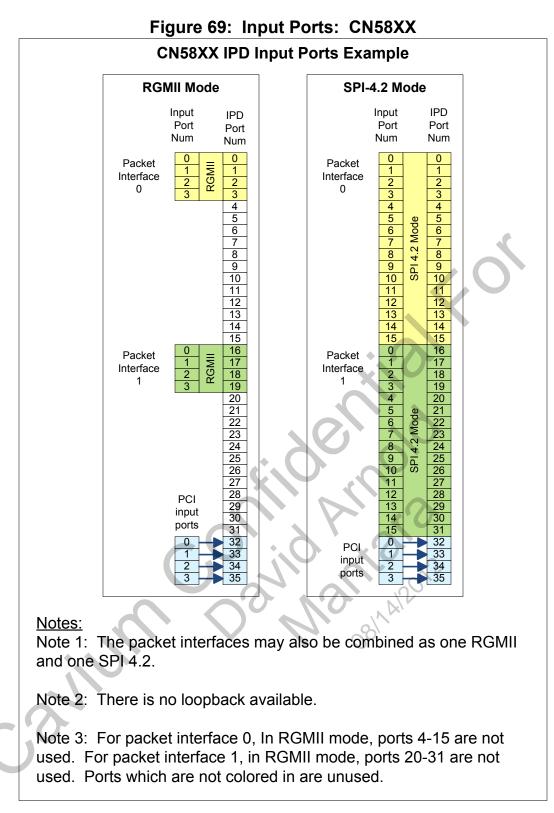

| Figure 69: | Input Ports: CN58XX                                       | 179 |  |

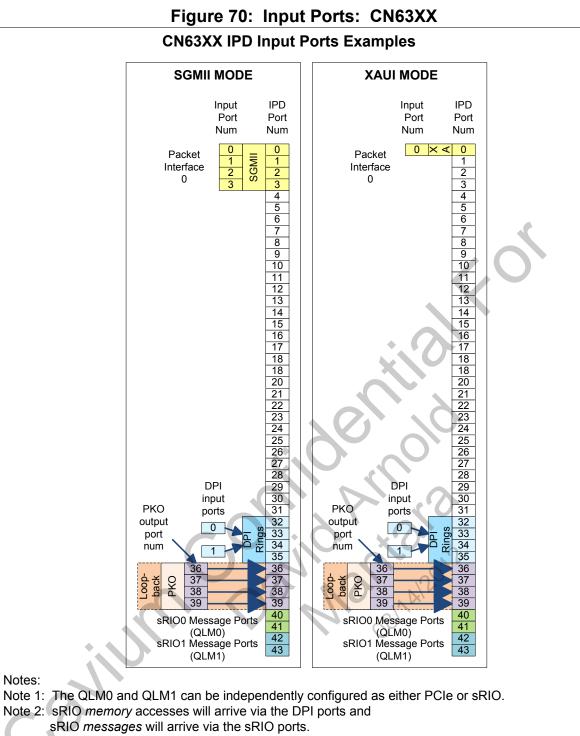

| Figure 70: | Input Ports: CN63XX                                       |     |  |

|            |                                                           |     |  |

PIP and IPD

# 1 Introduction

In the *Packet Flow* chapter of the *OCTEON Programmer's Guide (The Fundamentals)*, the actions performed by the Packet Input Processor (PIP) and Input Packet Data (IPD) are shown with minimal details. This chapter provides in depth detail of the processing performed by these two units, and how to customize their configuration to optimize throughput.

Together, PIP/IPD:

- 1. Parse the packet, checking for errors in L2/L3 headers

- 2. Provide congestion control: drop packet and/or backpressure as needed

- 3. Create a Work Queue Entry (WQE) for the packet if it is not dropped

- 4. Determine packet properties which affect subsequent scheduling actions by the SSO (POW) (Group, QoS, Tag Type, Tag Value)

- 5. Store the packet data

- 6. Send the WQE to the SSO for scheduling

The PIP/IPD provides a tremendous amount of configuration flexibility. Correct configuration of the PIP/IPD requires a clear view of the desired software architecture and specifics of the target application. Before reading this chapter, it is essential to understand the contents of the *Packet Flow* chapter. It is also helpful to read the *Software Overview* chapter (especially the *Software Architecture* section), the *Essential Topics, Configuration, Advanced Topics,* and the *Free Pool Allocator (FPA)* chapters These chapters help the user visualize the overall system necessary to develop a customized solution which will best fit the target application. The PIP/IPD is a central component of that customized solution.

Because of the feature-richness flexibility of the PIP and IPD units, the chapter describing these features is quite extensive. The chapter is designed so that readers can select the relevant section their specific application, and ignore sections discussing unused features.

Although the PIP and IPD are separate units, they are so closely associated that they are collected into a pseudo-block, the Packet Input (PKI) block. This pseudo-block is only used in high-level diagrams, and is not used in the text of this chapter.

The PIP/IPD works closely with:

- The Packet Input Interfaces

- The Free Pool Allocator (FPA)

- The Schedule Synchronization Order (SSO) unit. (The SSO unit is referred to as the Packet Order Work unit, or POW in the *Hardware Reference Manual*.)

The PIP/IPD receives the packet data from a traffic ingress port (for example, GMII). By using configuration information from PIP/IPD Configuration and Status Registers (CSRs), and from parsing the packet header, PIP/IPD determines the essential packet scheduling information: QoS level, Work Group ID, Tag Value, and Tag Type. The PIP/IPD creates a Work Queue Entry (WQE) and forwards it to the SSO. PIP/IPD stores the packet data in L2/DRAM, using a dedicated bus to the I/O Bridge (IOB). If necessary, congestion control is managed via backpressure or RED.

The FPA maintains two pools of buffers: the Packet Data buffer pool and the Work Queue Entry buffers. Packet Data buffers and WQE buffers are automatically allocated from the appropriate FPA pool by PIP/IPD. The size and quantity of buffers, and the WQE buffer pool number are configured when Simple Executive is configured at build time. The Packet Data buffer pool is required by hardware to be FPA pool 0. The pool number not a configurable option. See the *Essential Topics, Configuration,* and *FPA* chapters for details.

The IPD is responsible for:

- If required by PIP/IPD congestion control mechanisms, backpressure ports

- If no backpressure, IPD is responsible for receiving the packet from the input ports

- If required by configurable congestion control mechanisms, drop the packet, otherwise continue packet processing

- Allocating the Work Queue Entry buffer from the WQE buffer pool maintained by the FPA

- Allocating the Packet Data buffers from the Packet Data buffer pool in maintained by the FPA

- Storing information in the Work Queue Entry, including the QoS queue, Work Group, Tag Type, and Tag Value which are computed by the PIP

- Storing information in the Packet Data Buffer(s) as needed

- Writing the Packet Data Buffer(s) to L2/DRAM

- Performing the add\_work operation to add the Work Queue Entry to the appropriate Quality of Service (QoS) queue in the SSO

The PIP is responsible for:

- Packet parsing

- Perform optional checks on the packet

- Compute the QoS queue, Work Group, Tag Type, and Tag Value

- Provide QoS, Work Group, Tag Type, and Tag Value information to IPD

The OCTEON Software Development Kit supports the PIP/IPD units with a thin layer of software designed to serve as a base for more complex customized development. Because of the rich features provided by the PIP/IPD units, the API does not cover all possible uses. This chapter provides an overview of the API and the details needed to get started with customization.

The *CN54/55/56/57 Hardware Reference Manual* (*HRM*) was used to create many of the examples in this document. Different processors have slight differences in implementation, primarily in ports and interfaces supported. Whenever information in the *HRM* conflicts with information in this chapter, it is assumed that the *HRM* is more correct.

The *HRM* is an essential reference when writing customized software for the PIP/IPD units. This chapter is not intended to replace the *HRM*.

In this chapter, most register information matches the OCTEON CN55/55/56/57XX processor *HRM*, with some additions for CN63XX.

Note that in most cases the format REGISTER[FIELD] in this chapter refers to a hardware register and field combination, not a software ARRAY[INDEX].

The following figure is from the *Packet Flow* chapter. This figure provides a high-level view the packet flow through the system. Proper configuration of PIP/IPD is essential for high-performance systems.

1A2012

Figure 1: Overview of PIP/IPD Processing

The I/O Bus consists of two buses: IOBI (input) and IOBO (output). Received packet data goes directly from Interface RX to IPD on IOBI without going through IOB. (IPD is a second sink on the bus.)

1. After the Interface Rx Port receives the packet and checks it for errors, it passes the packet to the Input Packet Data (IPD) Unit (via the IOBI). The IPD shares the data with the Packet Input Processor (PIP). These two units work together to process the input packet.

2. After the PIP performs the packet parsing, including any checks configured by software, it computes the data needed by the IPD for the Work Queue Entry (WQE) Fields (Group, Tag Type, Tag Value, and QoS).

3. If IPD does not drop the packet, it allocates a WQE buffer and Packet Data buffer from the Free Pool Allocator (FPA) Unit. (The FPA manages the free buffers.)

4. The IPD writes the WQE fields to the WQE Buffer, and writes the packet data to the Packet Data buffer in L2/DRAM (DMA via IPDB).

5. The IPD performs the **add\_work** operation to add the WQE Pointer to the appropriate QoS queue in the Schedule Synchronization Order (SSO) Unit.

# PIP and IPD

# 2 Simple Executive Configuration and APIs

The PIP/IPD API supplied with the SDK does not cover all possible uses of the two units. This section provides an overview of the SDK 1.9.0 API, with some new features from SDK 2.0.

Most users take the default configuration provided by Simple Executive. The configuration can be customized (see the directions in the *Configuration* chapter, the *Free Pool Allocator (FPA)* chapter, and in this chapter).

An example of using the API functions is in Section 18 – "Appendix E: Example Code (linux-filter)".

Most applications will use the API as follows:

- 1) Define CVMX\_HELPER\_ENABLE\_IPD=0 // allows user to control when initialization is considered to be complete

- 2) Call cvmx\_helper\_initialize\_fpa() to setup the FPA pools.

- 3) Call cvmx helper initialize packet io global () once on only one core

- 4) Call cvmx\_helper\_initialize\_packet\_io\_local() on each core. This will get all packet IO running.

- 5) Call the cvmx\_pip\* or cvmx\_ipd\* functions only to change (modify) the IPD/PIP defaults as needed. (For example, call cvmx pip config port().)

- 6) Call cvmx\_helper\_ipd\_and\_packet\_input\_enable()

| Table 1: Summary of R                                                                                                                                           | elevant Functions                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                             |

| Helper Functions                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                         |

| <pre>cvmx_helper_initialize_packet_io_global() cvmx_helper_initialize_packet_io_local() cvmx_helper_ipd_and_packet_input_enable() cvmx_helper_setup_red()</pre> | Initialize global PIP/IPD variables. This<br>function calls cvmx_ipd_config()<br>using values defined in executive-<br>config.h.<br>Each core calls this after global<br>initialization routine is complete<br>Call once all initialization is complete<br>Configure Per-QoS RED for congestion<br>control (all queues will have the same pass<br>and drop thresholds). |

| <pre>cvmx_helper_setup_red_queue()</pre>                                                                                                                        | Configure Per-QoS RED or WRED for<br>congestion control (each queue can have<br>different pass and drop thresholds). Call<br>cvmx_helper_setup_red() first, then<br>call this function to modify queue<br>thresholds as needed.                                                                                                                                         |

#### Table 1: Summary of Relevant Functions

| Function                                           | Description                                                                                                                                                            |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>cvmx_helper_shutdown_packet_io_global()</pre> | (New in SDK 2.0). This function is used<br>to shutdown the packet handling units,<br>including IPD.                                                                    |

| <pre>cvmx_helper_shutdown_packet_io_local()</pre>  | (New in SDK 2.0.) This function does a core-local shutdown of packet I/O after the global shutdown is complete.                                                        |

| PIP Functions                                      | 1                                                                                                                                                                      |

| <pre>cvmx_pip_config_port()</pre>                  | Configure a PIP/IPD input port.                                                                                                                                        |

| <pre>cvmx_pip_config_crc()</pre>                   | Configure the hardware CRC engine (on some processors).                                                                                                                |

| cvmx pip tag mask clear ()                         | Clear all bits in a tag mask.                                                                                                                                          |

| <pre>cvmx_pip_tag_mask_set()</pre>                 | Set bits in the selected tag mask (used to create tag value)                                                                                                           |

| cvmx pip config vlan qos()                         | Configure VLAN-to-QoS Table 0                                                                                                                                          |

| cvmx pip config diffserv qos()                     | Configure Diffserv-to-QoS table                                                                                                                                        |

| cvmx pip get port status()                         | Get port statistics                                                                                                                                                    |

| IPD Functions                                      |                                                                                                                                                                        |

| <pre>cvmx_ipd_config()</pre>                       | Configure global settings for IPD.                                                                                                                                     |

| <pre>cvmx_ipd_enable(void)</pre>                   | This function is used to enable the IPD if<br>Simple Executive is configured to not<br>enable IPD.                                                                     |

| <pre>cvmx_ipd_disable(void)</pre>                  | Instead of calling this function, use the<br>new SDK 2.0 function<br>cvmx_helper_shutdown_packet_io_<br>global(), which calls<br>cvmx_ipd_disable() at the right time. |

| cvmx_ipd_disable(void)                             | 08/14/2                                                                                                                                                                |

# 2.1 Simple Executive Configuration

PIP and IPD depend on proper configuration of Simple Executive defines and FPA pool configuration.

In addition to the pools, the following Simple Executive Configuration variables are applicable to PIP/IPD:

| Define                                                  | Purpose                                                                                                                                                                                                                                                                                                             | Default<br>Value      |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| PIP/IPD Configuration variables defined in e.<br>order) |                                                                                                                                                                                                                                                                                                                     |                       |

| CVMX_ENABLE_HELPER_FUNCTIONS                            | Enables essential functions such as<br><pre>cvmx_helper_initialize_fpa()</pre> . We strongly recommend use of the<br>helper functions.                                                                                                                                                                              | Un-<br>defined        |

| CVMX_ENABLE_LEN_M8_FIX                                  | Enable fix for the known issue PKI-<br>100 ("Size field is 8 too large in the<br>WQE and next pointers"). If this<br>variable is set to 0, the fix for this<br>known issue will not be enabled.                                                                                                                     | 1                     |

| CVMX_HELPER_ENABLE_BACK_PRESSURE                        | We strongly recommend use of this backpressure feature.                                                                                                                                                                                                                                                             | 1                     |

| CVMX_HELPER_ENABLE_IPD                                  | This will cause the IPD to be enabled<br>after initialization. Once IPD is enabled,<br>the hardware will start accepting packets.<br>If configuration changes are made from<br>the default, then set this configuration<br>variable to 0 and, after custom changes<br>are complete, then call<br>cvmx_ipd_enable(). | 1                     |

| CVMX_HELPER_FIRST_MBUFF_SKIP                            | The number of bytes to reserve before<br>the start of the packet in the MBUF.                                                                                                                                                                                                                                       | 184<br>(See<br>Note1) |

| CVMX_HELPER_INPUT_PORT_SKIP_MODE                        | Select either skip-to-L2, skip-to-IP, or uninterpreted.                                                                                                                                                                                                                                                             | See<br>Note2          |

| CVMX_HELPER_INPUT_TAG_INPUT_PORT                        | Use input port value in tag value creation.                                                                                                                                                                                                                                                                         | 1                     |

| CVMX_HELPER_INPUT_TAG_IPV4_DST_IP                       | Use IPv4 Destination IP address field in tag value creation.                                                                                                                                                                                                                                                        | 0                     |

| CVMX_HELPER_INPUT_TAG_IPV4_DST_PORT                     | Use IPv4 Destination Port field in tag value creation.                                                                                                                                                                                                                                                              | 0                     |

| CVMX_HELPER_INPUT_TAG_IPV4_PROTOCOL                     | Use IPv4 Protocol field in tag value creation.                                                                                                                                                                                                                                                                      | 0                     |

#### Table 2: Simple Executive PIP/IPD Configuration Variables

| Define                                   | Purpose                                                                                   | Default<br>Value |

|------------------------------------------|-------------------------------------------------------------------------------------------|------------------|

| CVMX_HELPER_INPUT_TAG_IPV4_SRC_IP        | Use IPv4 Source IP address field in tag value creation.                                   | 0                |

| CVMX_HELPER_INPUT_TAG_IPV4_SRC_PORT      | Use IPv4 Source Port field in tag value creation.                                         | 0                |

| CVMX_HELPER_INPUT_TAG_IPV6_DST_IP        | Use IPv6 Destination IP address field in tag value creation.                              | 0                |

| CVMX_HELPER_INPUT_TAG_IPV6_DST_PORT      | Use IPv6 Destination Port field in tag value creation.                                    | 0                |

| CVMX_HELPER_INPUT_TAG_IPV6_NEXT_HEADER   | Use IPv6 Next Header field in tag value creation.                                         | 0                |

| CVMX_HELPER_INPUT_TAG_IPV6_SRC_IP        | Use IPv6 Source IP address field in tag value creation.                                   | 0                |

| CVMX_HELPER_INPUT_TAG_IPV6_SRC_PORT      | Use IPv6 Source Port field in tag value creation.                                         | 0                |

| CVMX_HELPER_INPUT_TAG_TYPE               | Either ORDERED, ATOMIC, or NULL.                                                          | See<br>Note3     |

| CVMX_HELPER_NOT_FIRST_MBUFF_SKIP         | The number of bytes to reserve in each chained packet buffer (MBUF) after the first MBUF. | 0                |

| Notes                                    |                                                                                           |                  |

| Notel. The default CVMX HELPER FIRST MBD | IFF SKIP value in the base SDK is set to                                                  |                  |

*Note1:* The default CVMX\_HELPER\_FIRST\_MBUFF\_SKIP value in the base SDK is set to 184 for compatibility with IPSEC to allow header expansion.

- Note2: The default value for CMVX\_HELPER\_INPUT\_PORT\_SKIP\_MODE is CVMX\_PIP\_PORT\_CFG\_MODE\_SKIPL2. See cvmx\_pip\_port\_parse\_mode\_t in cvmx-csr-enums.h.

- Note3: The default value for CVMX\_HELPER\_INPUT\_TAG\_TYPE is CVMX\_POW\_TAG\_TYPE\_ORDERED.

#### 2.1.1 About FPA Pools

In most applications, two FPA pools are used by PIP/IPD:

- The FPA Pool used for Packet Data Buffers is always FPA Pool 0

- The FPA pool used for Work Queue Entry (WQE) buffers is configurable, but is typically FPA Pool 1

FPA pool configuration information is provided in the *Free Pool Allocator (FPA)* chapter. If the default configuration will be changed, it is essential to read the *FPA* chapter. Pool information is summarized in this section.

The default pool configuration used in the SDK is shown in the following table.

| _        |

|----------|

| $\frown$ |

|          |

|          |

|          |

| d        |

| Ŭ        |

|          |

| 66       |

| <u> </u> |

|          |

|          |

|          |

#### Table 3: Default FPA Pool Configuration

| Item                                                                                                                                                    | Default Value                                             |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|

| Packet Data Buffers                                                                                                                                     |                                                           |  |

| Pool Name                                                                                                                                               | CVMX_FPA_PACKET_POOL                                      |  |

| Description String                                                                                                                                      | "Packet buffers"                                          |  |

| Pool Number (Default value)                                                                                                                             | 0 (cannot be changed)                                     |  |

| Default Buffer Size                                                                                                                                     | 16 * cache line size (2048 bytes) - See Note1, Note2      |  |

| Default Number of Buffers                                                                                                                               | Configurable via cvmx_helper_initialize_fpa() - See Note3 |  |

| Protected / Permanent                                                                                                                                   | 1 (TRUE)                                                  |  |

| Work Queue Entry Buffers                                                                                                                                |                                                           |  |

| Name                                                                                                                                                    | CVMX_FPA_WQE_POOL                                         |  |

| Description String                                                                                                                                      | "Work queue entries"                                      |  |

| Pool Number (Default value)                                                                                                                             | 1 (This can be any number; it is set to 1 by convention)  |  |

| Default Buffer Size                                                                                                                                     | 1 * cache line size (128 bytes) – See Note1, Note2        |  |

| Default Number of Buffers                                                                                                                               | Usually the same as the number of Packet Data Buffers     |  |

| Protected / Permanent                                                                                                                                   | 1 (TRUE)                                                  |  |

| Notes                                                                                                                                                   |                                                           |  |

| Note1: Buffer Size must be a minimum of 128 bytes (cache line size), and must be a multiple of 128 bytes (CVMX_FPA_MIN_BLOCK_SIZE, CVMX_FPA_ALIGNMENT). |                                                           |  |

Note2: The default buffer size is configured in cvmx-resources.config

*Note3: See the* passthough *example code*.

The following tables provide the PIP/IPD perspective on the Packet Data Buffers and Work Queue Entry buffers.

# Table 4: Packet Data Buffers Information

Packet Data Buffers

#### **Unit Allocating Buffer**

The IPD automatically allocates Packet Data Buffers. Packet Data Buffers are always in FPA pool 0: this is not configurable.

#### What controls the buffer allocation and use?

In the Simple Executive, the function cvmx\_helper\_global\_setup\_ipd() sets the value of IPD\_PACKET\_MBUFF\_SIZE[MB\_SIZE]. This value must match the size of the buffers in FPA pool 0. The IPD always allocates Packet Data Buffers from pool 0.

#### Packet Data Buffers

#### **Recommended Buffer Size**

Up to 2048 bytes (sixteen cache lines) (MTU of 1500 bytes).

#### **Recommended Number of Buffers**

Either 4096 or the maximum number of in-flight packets.

#### Unit Freeing Buffer

PKO or core software

#### How does the system know which pool the buffer should be returned to?

The originating FPA pool number is stored automatically in the Work Queue Entry data structure by the IPD. The PKO will optionally free the buffer to the specified pool (always Pool 0 for Packet Data Buffers). The core may also optionally free the Packet Data Buffer.

#### Table 5: Work Queue Entry Buffers Information

Work Queue Entry (WQE) Buffers

#### **Unit Allocating Buffer**

The IPD or the core (via software). The IPD automatically allocates WQE buffers.

#### What controls the buffer allocation and use?

In the Simple Executive, the function cvmx\_helper\_global\_setup\_ipd() sets the value of IPD\_WQE\_FPA\_QUEUE[WQE\_QUE]. This register field is used to specify which FPA pool the Work Queue Entry comes from.

#### **Recommended Buffer Size**

128 bytes (one cache line)

#### **Recommended Number of Buffers**

At least as many as Packet Data Buffers. If dynamic shorts are enabled, then packets which can fit entirely in the space reserved in the WQE will not also have a duplicate copy in the Packet Data Buffer. In the case where the WQE is in a WQE buffer (the option to have it in the Packet Data Buffer is not enabled), then the Packet Data Buffer will not exist for dynamic shorts, and more WQE Buffers will be needed than Packet Data Buffers.

#### **Unit Freeing Buffer**

Core software is responsible for freeing the buffer.

#### How does software know which pool the buffer should be returned to?

When freeing a WQE Buffer, use the define provided by the Simple Executive: CVMX\_FPA\_WQE\_POOL

2.2

# Helper Functions

These functions simplify configuring and using the PIP/IPD.

#### Table 6: Helper Functions

| Induce 6. Helper Functions                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Helper API Functions                                                                                                                                                                                                                                                                                  |

| int cvmx_helper_initialize_packet_io_global(void)                                                                                                                                                                                                                                                     |

| Initialize global PIP/IPD variables. It initializes the PIP, IPD, and PKO hardware to support simple priority based queues for the Ethernet ports. Each port is configured with a number of priority queues based on CVMX_PKO_QUEUES_PER_PORT_* where each queue is lower priority than the previous. |

| Returns 0 on success, otherwise returns non-zero. This function calls cvmx ipd config()                                                                                                                                                                                                               |

| using values defined in executive-config.h.                                                                                                                                                                                                                                                           |

| <pre>int cvmx_helper_initialize_packet_io_local(void)</pre>                                                                                                                                                                                                                                           |

| Each core calls this after global initialization routine is complete. Returns 0 on success, otherwise returns non-zero.                                                                                                                                                                               |

| <pre>int cvmx_helper_ipd_and_packet_input_enable(void)</pre>                                                                                                                                                                                                                                          |

| Called after all internal packet IO paths are setup. This function enables IPD/PIP and begins                                                                                                                                                                                                         |

| packet input and output.                                                                                                                                                                                                                                                                              |

| Returns 0 on success, otherwise returns non-zero.                                                                                                                                                                                                                                                     |

| <pre>int cvmx_helper_setup_red(int pass_thresh, int drop_thresh)</pre>                                                                                                                                                                                                                                |

| Configure Per-QoS RED for congestion control (all queues will have the same pass and drop                                                                                                                                                                                                             |

| thresholds). The arguments are:                                                                                                                                                                                                                                                                       |

| pass_thresh: the HIGH watermark (if the number of available Packet Data Buffers                                                                                                                                                                                                                       |

| is > pass_thresh, the packet is admitted)                                                                                                                                                                                                                                                             |

| drop_thresh: the LOW watermark (if the number of available Packet Data buffers<br>is <= drop_thresh, all incoming packets are dropped                                                                                                                                                                 |

| If pass_thresh >= number of available buffers > drop_thresh, packets are randomly                                                                                                                                                                                                                     |

| dropped.                                                                                                                                                                                                                                                                                              |

| <pre>cvmx_helper_setup_red_queue(int queue, int pass_thresh, int drop_thresh)</pre>                                                                                                                                                                                                                   |

| Configure Per-QoS RED or WRED for congestion control (each queue can have different pass<br>and drop thresholds). Call cvmx_helper_setup_red() first, then call this function to<br>modify queue thresholds as needed. The arguments are:<br>queue: which QoS queue's watermarks to set               |

| pass thresh: the HIGH watermark (if the number of available Packet Data Buffers                                                                                                                                                                                                                       |

| is > pass thresh, the packet is admitted)                                                                                                                                                                                                                                                             |

| drop_thresh: the LOW watermark (if the number of available Packet Data buffers                                                                                                                                                                                                                        |

| is <= drop_thresh, all incoming packets are dropped                                                                                                                                                                                                                                                   |

| <pre>If pass_thresh &gt;= number of available buffers &gt; drop_thresh, packets are randomly dropped.</pre>                                                                                                                                                                                           |

#### Helper API Functions

int cvmx\_helper\_shutdown\_packet\_io\_global(void)

New in SDK 2.0. This function is used to undo the the initialization performed in cvmx\_helper\_initialize\_packet\_io\_global(). After calling this routine and the local version on each core, packet IO for the OCTEON processor will be disabled and placed in the initial reset state. It will then be safe to call the initialization function later on. Note that this routine does not empty the FPA pools. It frees all buffers used by the packet IO hardware to the FPA so a function emptying the FPA after shutdown should find all packet buffers in the FPA.

Returns 0 on success, negative on failure.

int cvmx\_helper\_shutdown\_packet\_io\_local(void)

New in SDK 2.0. This function does a core-local shutdown of packet I/O and should be called on each core after calling cvmx\_helper\_shutdown\_packet\_io\_global(). Returns 0 on success, negative on failure.

11A12017

## 2.3 **PIP Functions**

These functions can be used to change the default configuration created by the helper routines.

| Table 7: PIP Functions                                                                                                                                                                            |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIP API Functions (cvmx-pip.h)                                                                                                                                                                    |  |  |  |  |  |

| <pre>void cvmx_pip_config_port(uint64_t port_num,<br/>cvmx_pip_port_cfg_t port_cfg, cvmx_pip_port_tag port_tag_cfg)</pre>                                                                         |  |  |  |  |  |

| Configure an Ethernet input port. The arguments are:<br>port_num: The port number to configure                                                                                                    |  |  |  |  |  |

| <pre>port_cfg: a data structure containing the configuration information port_tag_cfg: a data structure containing the port's tag configuration information</pre>                                 |  |  |  |  |  |

| <pre>void cvmx pip config crc(uint64 t interface, uint64 t invert result,<br/>uint64_t reflect, uint32_t initialization_vector)</pre>                                                             |  |  |  |  |  |

| Configure the hardware CRC engine. The arguments are:<br>interface: Interface to configure (0 or 1)<br>invert_result: Invert the result of the CRC<br>reflect: Reflect                            |  |  |  |  |  |

| initialization_vector: CRC initialization vector                                                                                                                                                  |  |  |  |  |  |

| <pre>cvmx_pip_tag_mask_clear (uint64_t mask_index)</pre>                                                                                                                                          |  |  |  |  |  |

| Clear all bits in a tag mask. This function should be called on startup before any calls to                                                                                                       |  |  |  |  |  |

| <pre>cvmx_pip_tag_mask_set(). Each bit set in the final mask represents a byte used in the<br/>packet for tag generation. The argument is:</pre>                                                  |  |  |  |  |  |

| mask index: Which tag mask to clear (03)                                                                                                                                                          |  |  |  |  |  |

| cvmx pip tag mask set (uint64 t mask index, uint64 t offset,                                                                                                                                      |  |  |  |  |  |

| uint64_t len)                                                                                                                                                                                     |  |  |  |  |  |

| The tag mask is used when the cvmx_pip_port_tag_cfg_t tag_mode is non zero. There are four separate masks that can be configured. The arguments are:<br>mask index: which tag mask to modify (03) |  |  |  |  |  |

| offset: offset into the bitmask to set bits at. Use the GCC macro offsetof() to determine                                                                                                         |  |  |  |  |  |

| the offsets into packet headers. For example, offsetof (ethhdr, protocol) returns the                                                                                                             |  |  |  |  |  |

| offset of the ethernet protocol field. The bitmask selects which bytes to include the tag, with bit                                                                                               |  |  |  |  |  |

| offset X selecting byte at offset X from the beginning of the packet data.                                                                                                                        |  |  |  |  |  |

| len: Number of bytes to include. Usually this is the sizeof() the field.                                                                                                                          |  |  |  |  |  |

|                                                                                                                                                                                                   |  |  |  |  |  |

| <pre>void cvmx_pip_config_vlan_qos(uint64_t vlan_priority, unit64_t qos)</pre>                                                                                                                    |  |  |  |  |  |

| Configures the VLAN priority to QOS mapping for VLAN-to-QOS Table0. Note there is no                                                                                                              |  |  |  |  |  |

| function to configure VLAN-to-QOS Table1. The arguments are:                                                                                                                                      |  |  |  |  |  |

| vlan_priority: 0-7                                                                                                                                                                                |  |  |  |  |  |

| qos: QOS value to assign to incoming packets with VLAN priority matching this VLAN priority.                                                                                                      |  |  |  |  |  |

|                                                                                                                                                                                                   |  |  |  |  |  |

void cvmx\_pip\_config\_diffserv\_qos(unit64\_t diffserv, unit64\_t qos)

Configures the Diffserv to QOS mapping. Note this function does not enable Diffserv QOS for the port. The arguments are:

diffserv: diffserv field value (0-63)

qos: QOS value to assign to incoming packets with Diffserv value matching this Diffserv field value.

void cvmx\_pip\_get\_port\_status(unit64\_t port\_num, uint64\_t clear, cvmx\_pip\_port\_status\_t \*status)

Get the statistics for a port. The arguments are:

port\_num: the port number

clear: whether to clear the values after reading them (1=clear, 0=do not clear)  $\triangleleft$

status: the data structure used to store the status

On success, this function retrieves the port status and stores it in the status data structure.

## 2.4 PIP Data Structures and Defines

#### 2.4.1 The cvmx\_pip\_port\_cfg\_t Data Structure

This data structure is used to specify the configuration parameters for each port. The contents of the data structure vary with the processor model. See cvmx\_pip\_port\_cfgx\_t in cvmx-csr-typedefs.h in the SDK for details.

#### 2.4.2 The cvmx\_pip\_port\_tag\_cfg\_t Data Structure

This data structure is used to specify the tag configuration parameters for each port. The contents of the data structure vary with the processor model. See cvmx\_pip\_port\_tag\_cfgx\_t in cvmx-csr-typedefs.h in the SDK for details.

# 2.4.3 The cvmx\_pip\_parse\_mode\_t Defines (Parse Modes for Incoming Packets)

These defines (enumerated in cvmx\_pip\_parse\_mode\_t) are used to set the parse mode for the incoming packet:

CVMX\_PIP\_PORT\_CFG\_MODE\_NONE = 0ull, // Uninterpreted CVMX\_PIP\_PORT\_CFG\_MODE\_SKIPL2 = 1ull, // Skip-to-L2 CVMX\_PIP\_PORT\_CFG\_MODE\_SKIPIP = 2ull // Skip-to-IP

#### 2.4.4 The cvmx\_pip\_tag\_mode\_t Defines (control the initial SSO Tag Value)

These defines (enumerated in cvmx\_pip\_tag\_mode\_t) are used to set the initial Tag Value for the incoming packet:

```

CVMX_PIP_TAG_MODE_TUPLE = Oull,// Always use tuple tag algorithm.CVMX_PIP_TAG_MODE_MASK = 1ull,// Always use mask tag algorithmCVMX_PIP_TAG_MODE_IP_OR_MASK = 2ull,// If packet is IP, use tuple else

```

// use mask

CVMX\_PIP\_TAG\_MODE\_TUPLE\_XOR\_MASK = 3ull // tuple XOR mask

#### 2.4.5 The cvmx\_pow\_tag\_type\_t Defines (control the initial SSO Tag Type)

These defines (enumerated in cvmx\_pow\_tag\_type\_t) are used to set the initial Tag Type for the incoming packet: