## Free Pool Allocator (FPA)

## TABLE OF CONTENTS

| LIST OF TABLES       4         Introduction       4         Introduction       6         2 Overview of FPA.       7         2.1 Functional Overview       7         2.2 Hardware Blocks Which Use FPA-Managed Buffers       7         2.3 Operations.       10         2.4 FPA Registers       10         2.5 Using the FPA.       11         2.5.1 Configure the FPA Unit       11         2.5.2 Initialize the FPA Unit       11         2.5.3 Enable the FPA Unit       11         2.5.4.1 Allocating Memory for FPA-Managed Buffers       11         3.1 Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2.1 Rules       13         3.2.2 Is There a Limit on the Number of Buffers?       14         3.2.3 Can a Pool Contain Different-Sized Buffers?       14         3.2.4 Can More Buffers be Added to a Buffer Pool at Any Time?       14         3.2.5 Configurating Buffers from Linux and the Affect on Buffer Size       15         3.2.6 Allocating Buffers Size       17         4.1 Packet Data Buffer Count       19         4.2.1.1 What if the Formula Yields a Negative Number?       11         4.2.2 Packet Data Buffer Count       19         4.2.1.3 What if the System Runs Out of Available      | TABLE OF CONTENTS                                                   | 1  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----|

| 1       Introduction       6         2       Overview of FPA       7         2.1       Functional Overview       7         2.2       Hardware Blocks Which Use FPA-Managed Buffers       7         2.3       Operations       10         2.4       FPA Registers       10         2.5       Using the FPA       11         2.5.1       Configure the FPA Unit       11         2.5.2       Initialize the FPA Unit       11         2.5.3       Enable the FPA Unit       11         2.5.4       Populate the FPA Pools       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2.1       Rules       13         3.2.2       Is There a Limit on the Number of Buffers?       14         3.2.3       Can a Pool Contain Different-Sized Buffers?       14         3.2.4       Can More Buffers be Added to a Buffer Pool at Any Time?       14         3.2.5       Configuring Hardware Units Which Automatically Use the Buffers       15         3.2.6       Allocating Buffers from L                                             | LIST OF TABLES                                                      | 4  |

| 2       Overview of FPA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |    |

| 2.1       Functional Overview       7         2.2       Hardware Blocks Which Use FPA-Managed Buffers       7         2.3       Operations.       10         2.4       FPA Registers       10         2.5       Using the FPA       11         2.5.1       Configure the FPA Unit.       11         2.5.2       Initialize the FPA Unit.       11         2.5.3       Enable the FPA Unit.       11         2.5.4       Populate the FPA Voit.       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         3.6       General Pool Configuration and Population Information.       12         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2.1       Rules       13         3.2.2       Is There a Limit on the Number of Buffers?       14         3.2.3       Can a Pool Contain Different-Sized Buffers?       14         3.2.4       Can More Buffers be Added to a Buffer Pool at Any Time?       14         3.2.5       Configuring Hardware Units Which Automatically Use the Buffers       15         3.2.6       Allocating Buffers from Linux and the Affect on Buffer Size       15<          | 1 Introduction.                                                     | 6  |

| 2.2       Hardware Blocks Which Use FPA-Managed Buffers       7         2.3       Operations       10         2.4       FPA Registers       10         2.5       Using the FPA       11         2.5.1       Configure the FPA Unit       11         2.5.2       Initialize the FPA Unit       11         2.5.3       Enable the FPA Unit       11         2.5.4       Populate the FPA Ools       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2       Configuration Overview       13       3.2.1         3.2.1       Rules       13       3.2.2         3.2.1       Rules       13       3.2.2         3.2       Configuring Hardware Units Which Automatically Use the Buffers       14         3.2.5       Configuring Hardware Units Which Automatically Use the Buffers       15         3.2.6       Allocating Buffers from Linux and the Affect on Buffer Size       15         3.2.6       Allocating Buffer Size<                            | 2 Overview of FPA                                                   | 7  |

| 2.3Operations102.4FPA Registers102.5Using the FPA112.5.1Configure the FPA Unit112.5.2Initialize the FPA Unit112.5.3Enable the FPA Unit112.5.4Populate the FPA Pools112.5.4.1Allocating Memory for FPA-Managed Buffers113.1Default Simple Executive Pool and Scratchpad Area Configuration123.2Configuration overview133.2.1Rules133.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size153.2.6Allocating Buffer Size164.1Packet Data Buffer Size174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1What if the Formula Yields a Negative Number?214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count214.2.3Wat if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers21                                                                                                                                                                                                        |                                                                     |    |

| 2.4       FPA Registers       10         2.5       Using the FPA.       11         2.5.1       Configure the FPA Unit.       11         2.5.2       Initialize the FPA Unit.       11         2.5.3       Enable the FPA Unit.       11         2.5.4       Populate the FPA Pools       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         3.6       General Pool Configuration and Population Information       12         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2       Configuration Overview       13         3.2.1       Rules       13         3.2.2       Is There a Limit on the Number of Buffers?       14         3.2.3       Can a Pool Contain Different-Sized Buffers?       14         3.2.4       Can More Buffers be Added to a Buffer Pool at Any Time?       14         3.2.5       Configuring Hardware Units Which Automatically Use the Buffers.       15         3.2.6       Allocating Buffers from Linux and the Affect on Buffer Size       15         3.2.6       Allocating Buffer Size       17         4.1       Packet Data Buffer Count.       19         4.2.1       Calculate the Maximum Number of Packet Data buffers Needed      | 2.2 Hardware Blocks Which Use FPA-Managed Buffers                   | 7  |

| 2.4       FPA Registers       10         2.5       Using the FPA.       11         2.5.1       Configure the FPA Unit.       11         2.5.2       Initialize the FPA Unit.       11         2.5.3       Enable the FPA Unit.       11         2.5.4       Populate the FPA Pools       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         3.6       General Pool Configuration and Population Information       12         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2       Configuration Overview       13         3.2.1       Rules       13         3.2.2       Is There a Limit on the Number of Buffers?       14         3.2.3       Can a Pool Contain Different-Sized Buffers?       14         3.2.4       Can More Buffers be Added to a Buffer Pool at Any Time?       14         3.2.5       Configuring Hardware Units Which Automatically Use the Buffers.       15         3.2.6       Allocating Buffers from Linux and the Affect on Buffer Size       15         3.2.6       Allocating Buffer Size       17         4.1       Packet Data Buffer Count.       19         4.2.1       Calculate the Maximum Number of Packet Data buffers Needed      | 2.3 Operations                                                      | 10 |

| 2.5       Using the FPA.       11         2.5.1       Configure the FPA Unit.       11         2.5.2       Initialize the FPA Unit.       11         2.5.3       Enable the FPA Unit.       11         2.5.4       Populate the FPA Pools       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         3       General Pool Configuration and Population Information.       12         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2       Configuration Overview       13         3.2.1       Rules       13         3.2.2       Is There a Limit on the Number of Buffers?       14         3.2.3       Can a Pool Contain Different-Sized Buffers?       14         3.2.4       Can More Buffers be Added to a Buffer Pool at Any Time?       14         3.2.5       Configuring Hardware Units Which Automatically Use the Buffers       15         3.2.6       Allocating Buffers from Linux and the Affect on Buffer Size       15         3.2.6       Allocata Buffer Count       19         4.2.1       Packet Data Buffer Size       18         4.2       Packet Data Buffer Size       19         4.2.1       Calculate the Maximum Number of Packet Data buffers Need | 2.4 FPA Registers                                                   | 10 |

| 2.5.1       Configure the FPA Unit.       11         2.5.2       Initialize the FPA Unit.       11         2.5.3       Enable the FPA Unit.       11         2.5.4       Populate the FPA Pools       11         2.5.4.1       Allocating Memory for FPA-Managed Buffers       11         3       General Pool Configuration and Population Information       12         3.1       Default Simple Executive Pool and Scratchpad Area Configuration       12         3.2       Configuration Overview       13         3.2.1       Rules       13         3.2.2       Is There a Limit on the Number of Buffers?       14         3.2.3       Can a Pool Contain Different Sized Buffers?       14         3.2.4       Can More Buffers be Added to a Buffer Pool at Any Time?       14         3.2.5       Configuring Hardware Units Which Automatically Use the Buffers       15         3.2.6       Allocating Buffers from Linux and the Affect on Buffer Size       15         4.1       Packet Data Buffer Size       17         4.1       Packet Data Buffer Size       18         4.2       Packet Data Buffer Count       19         4.2.1       Calculate the Maximum Number of Packet Data buffers Needed       19         4.2.1       Calculate th | 2.5 Using the FPA                                                   | 11 |

| 2.5.3Enable the FPA Unit112.5.4Populate the FPA Pools112.5.4.1Allocating Memory for FPA-Managed Buffers113General Pool Configuration and Population Information123.1Default Simple Executive Pool and Scratchpad Area Configuration123.2Configuration Overview133.2.1Rules133.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffer Size174.1Packet Data Buffer Size184.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.1Valuate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count214.2.3What if the Formula Yields a Negative Number?214.2.4Linux and Packet Data Buffer Count214.2.4Linux and Packet Data Buffer Count214.2.4Linux and Packet Data Buffer Count214.2.5WAt if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                             | 2.5.1 Configure the FPA Unit                                        | 11 |

| 2.5.4Populate the FPA Pools112.5.4.1Allocating Memory for FPA-Managed Buffers113General Pool Configuration and Population Information123.1Default Simple Executive Pool and Scratchpad Area Configuration123.2Configuration Overview133.2.1Rules133.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffer Size174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count214.2.4Linux and Packet Data Buffer Count214.2.4Linux and Packet Data Buffer Count214.2.4Linux and Packet Data Buffer Count214.2.5WQE Buffers23                                                                                                                                                                                                                         | 2.5.2 Initialize the FPA Unit                                       | 11 |

| 2.5.4.1Allocating Memory for FPA-Managed Buffers113General Pool Configuration and Population Information123.1Default Simple Executive Pool and Scratchpad Area Configuration123.2Configuration Overview133.2.1Rules133.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffer Size184.2Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the Formula Yields a Negative Number?214.2.4Linux and Packet Data Buffer Count214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                 | 2.5.3 Enable the FPA Unit                                           | 11 |

| 3General Pool Configuration and Population Information123.1Default Simple Executive Pool and Scratchpad Area Configuration123.2Configuration Overview133.2.1Rules133.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                             |                                                                     |    |

| 3.1Default Simple Executive Pool and Scratchpad Area Configuration123.2Configuration Overview133.2.1Rules133.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffer174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.5.4.1 Allocating Memory for FPA-Managed Buffers                   | 11 |

| 3.2Configuration Overview133.2.1Rules133.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size153.2.6Allocating Buffers174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3 General Pool Configuration and Population Information             | 12 |

| 3.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffers174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.1 Default Simple Executive Pool and Scratchpad Area Configuration | 12 |

| 3.2.2Is There a Limit on the Number of Buffers?143.2.3Can a Pool Contain Different-Sized Buffers?143.2.4Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffers174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.2 Configuration Overview                                          | 13 |

| 3.2.4 Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5 Configuring Hardware Units Which Automatically Use the Buffers153.2.6 Allocating Buffers from Linux and the Affect on Buffer Size154 Packet Data Buffers174.1 Packet Data Buffer Size184.2 Packet Data Buffer Count194.2.1 Calculate the Maximum Number of Packet Data buffers Needed194.2.2 Packet Data Buffer Count214.2.3 What if the Formula Yields a Negative Number?214.2.3 What if the System Runs Out of Available Packet Data Buffers?214.2.4 Linux and Packet Data Buffer Count215 WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.1 Rules                                                         | 13 |

| 3.2.4 Can More Buffers be Added to a Buffer Pool at Any Time?143.2.5 Configuring Hardware Units Which Automatically Use the Buffers153.2.6 Allocating Buffers from Linux and the Affect on Buffer Size154 Packet Data Buffers174.1 Packet Data Buffer Size184.2 Packet Data Buffer Count194.2.1 Calculate the Maximum Number of Packet Data buffers Needed194.2.2 Packet Data Buffer Count214.2.3 What if the Formula Yields a Negative Number?214.2.3 What if the System Runs Out of Available Packet Data Buffers?214.2.4 Linux and Packet Data Buffer Count215 WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.2 Is There a Limit on the Number of Buffers?                    | 14 |

| 3.2.5Configuring Hardware Units Which Automatically Use the Buffers153.2.6Allocating Buffers from Linux and the Affect on Buffer Size154Packet Data Buffers174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.2.3 Can a Pool Contain Different-Sized Buffers?                   | 14 |

| 3.2.6 Allocating Buffers from Linux and the Affect on Buffer Size154 Packet Data Buffers174.1 Packet Data Buffer Size184.2 Packet Data Buffer Count194.2.1 Calculate the Maximum Number of Packet Data buffers Needed194.2.1.1 What if the Formula Yields a Negative Number?214.2.2 Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3 What if the System Runs Out of Available Packet Data Buffers?214.2.4 Linux and Packet Data Buffer Count215 WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                     |    |

| 4Packet Data Buffers174.1Packet Data Buffer Size184.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.1What if the Formula Yields a Negative Number?214.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |    |

| 4.1Packet Data Buffer Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |    |

| 4.2Packet Data Buffer Count194.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.1.1What if the Formula Yields a Negative Number?214.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |    |

| 4.2.1Calculate the Maximum Number of Packet Data buffers Needed194.2.1What if the Formula Yields a Negative Number?214.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |    |

| 4.2.1.1What if the Formula Yields a Negative Number?214.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |    |

| 4.2.2Packet Data Buffer Count and PIP/IPD Congestion Control214.2.3What if the System Runs Out of Available Packet Data Buffers?214.2.4Linux and Packet Data Buffer Count215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                     |    |

| <ul> <li>4.2.3 What if the System Runs Out of Available Packet Data Buffers?</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |    |

| 4.2.4Linux and Packet Data Buffer Count.215WQE Buffers23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |    |

| 5 WQE Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |    |

| 5.2 WOE Buffer Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                     |    |

|    |                                                                                                                                                     | 24         |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| ~  | 5.3 Other Uses for WQE Buffers                                                                                                                      |            |

| 6  | PKO Command Buffers                                                                                                                                 |            |

|    | 6.1 PKO Command Buffer Size                                                                                                                         |            |

|    | 6.2 PKO Command Buffer Count                                                                                                                        |            |

| _  | 6.3 More Precise PKO Command Buffer Size and Count Calculations                                                                                     |            |

| 7  | Simple Executive API                                                                                                                                |            |

|    | 7.1 Limits and other Definitions                                                                                                                    |            |

|    | 7.2 Data Structures                                                                                                                                 |            |

|    | 7.2.1 The cvmx_fpa_pool_info_t (pool_info) Data Structure                                                                                           |            |

|    | 7.3 Easy-to-Use Executive FPA API Functions                                                                                                         | 29         |

|    | 7.3.1 Pool Information Functions                                                                                                                    | 30         |

|    | 7.3.1.1 Example Code: cvmx fpa get block size(),                                                                                                    |            |

|    | cvmx fpa get name().cvmx fpa get base()                                                                                                             | 31         |

|    | 7.3.1.2 Example Code: cvmx_fpa_is_member()                                                                                                          | 32         |

|    | 7.3.2 Easy-to-Use Initialize, Allocate, and Free Functions                                                                                          | 32         |

|    | 7.3.2.1 Example Code: cvmx_helper_initialize_fpa()                                                                                                  |            |

|    | 7.3.2.2 Example Code: cvmx_heiper_inicialize_ipa()                                                                                                  |            |

|    | 7.3.2.2 Example Code: CVIIX_IPa_aIIOC()                                                                                                             | 55         |

|    | 7.3.2.3 Example Code: cvmx_fpa_async_alloc()                                                                                                        | 36         |

|    | 7.3.2.4 Example Code: cvmx_fpa_free()                                                                                                               |            |

|    | 7.3.2.5 Example Code: cvmx_helper_free_packet_data()                                                                                                |            |

|    | 7.4 Advanced Functions                                                                                                                              | 38         |

|    | 7.4.1.1 cvmx_fpa_enable()                                                                                                                           | 39         |

|    | 7.4.1.2 Example Code: Calling cvmx fpa setup pool()                                                                                                 |            |

|    | 7.4.1.3 The cvmx_fpa_free_nosync() Function                                                                                                         | 40         |

|    | 7.4.1.4 Example Code: cvmx fpa shutdown pool()                                                                                                      |            |

| 8  | Basic Code Review Checklist                                                                                                                         | 42         |

| 9  | Basic Code Review Checklist                                                                                                                         | 12<br>44   |

| /  | 9.1 Buffer Organization                                                                                                                             | <br>11     |

|    | 9.2 In-Unit Buffer Address Cache (Address Cache)                                                                                                    |            |

|    | <ul> <li>9.2 In-Unit Buffer Address Cache (Address Cache)</li> <li>9.3 Watermarks for the In-Unit Buffer Address Cache</li> <li>Debugging</li></ul> |            |

| 1( | Debugging                                                                                                                                           | 49         |

| 10 | 10.1 Interrupts and Detected Error Conditions                                                                                                       | , 55<br>54 |

|    | 10.1.1 Permission Error (PERR)                                                                                                                      | 34<br>5 1  |

|    |                                                                                                                                                     | 34         |

|    | 10.1.2 Page Count Off (Incorrect) Error (COFF)                                                                                                      | 54         |

|    | 10.1.3 Underflow (UND)                                                                                                                              |            |

|    | 10.1.4 Single and Double Bit Memory Errors (SBE, DBE)                                                                                               |            |

|    | 10.2 Debugging and Status Information                                                                                                               |            |

|    | 10.3 Common Mistakes                                                                                                                                |            |

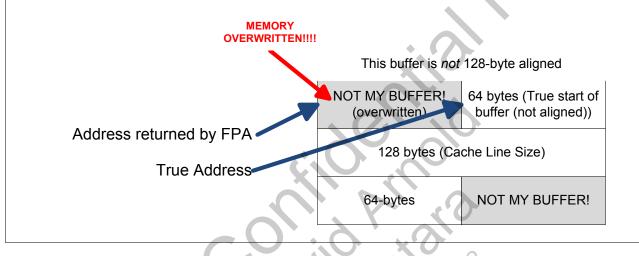

|    | 10.3.1 Buffer Alignment: Bad Alignment at Start of Buffer                                                                                           | 56         |

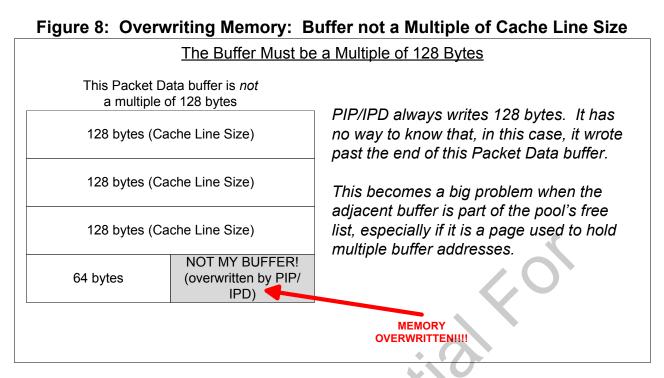

|    | 10.3.2 Buffer Alignment: Bad Alignment at End of Buffer                                                                                             | 56         |

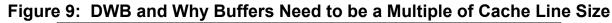

|    | 10.3.3 Buffer Size and Don't Write Back (DWB)                                                                                                       | 57         |

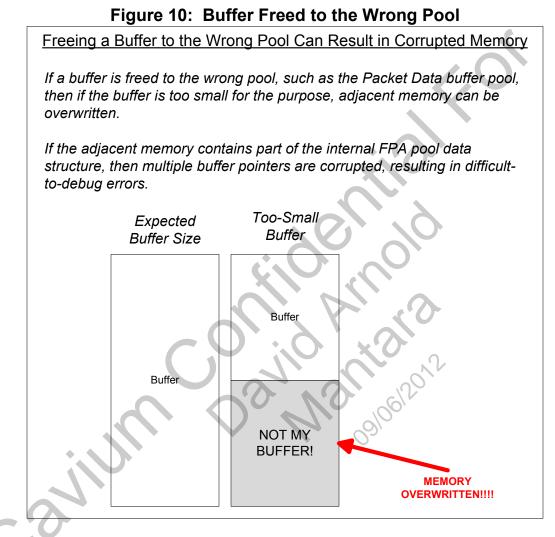

|    | 10.3.4 Buffer Freed to the Wrong Pool                                                                                                               |            |

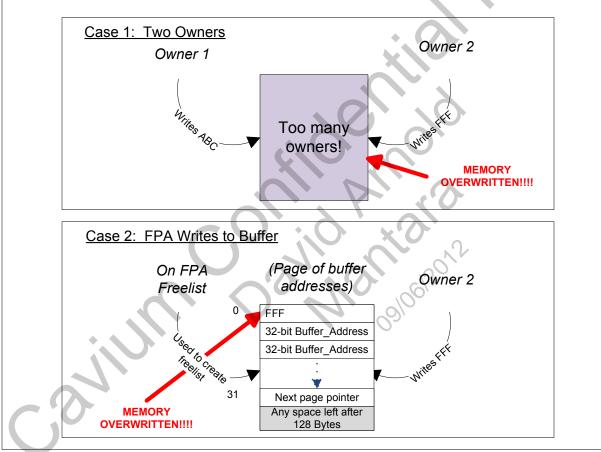

|    | 10.4 Buffer Freed More than Once                                                                                                                    |            |

| 11 | Performance Tuning                                                                                                                                  |            |

|    | 11.1 Enough Buffers                                                                                                                                 |            |

| 11.2   | Prefetch Buffers                                                | 61 |

|--------|-----------------------------------------------------------------|----|

| 11.3   | Initializing the Per-Pool Address Cache Allotment or Watermarks | 61 |

| 11.4   | Don't Write Back (DWB)                                          |    |

| 11.5   | Pool Number                                                     |    |

| 11.6   | Performance Tuning Checklist                                    |    |

| 12 Adv | vanced Code Review Checklist                                    | 64 |

| 13 Bey | ond the SDK – When not Using the Provided API                   | 65 |

| 13.1   | Design Considerations                                           | 65 |

| 13.2   | Enable the FPA and Populating the Pools                         | 65 |

| 13.3   | Synchronous Buffer Allocation                                   |    |

| 13.4   | Asynchronous Buffer Allocation                                  |    |

| 13.5   | Freeing a buffer                                                |    |

| 14 FPA | A Registers                                                     |    |

|        | figuring Units Which Allocate/Free FPA Buffers                  |    |

Nantara Nantara

0910612012

## LIST OF TABLES

| Table 1: Units Allocating/Freeing Buffer Addresses, or Accessing Buffers      | 9  |

|-------------------------------------------------------------------------------|----|

| Table 2: Default Simple Executive Pool Configuration                          |    |

| Table 3: Default Simple Executive Scratchpad Configuration                    |    |

| Table 4: Packet Data Buffers Overview                                         | 17 |

| Table 5: Packet Data Buffer Requirements                                      |    |

| Table 6: Work Queue Entry Buffers Overview                                    |    |

| Table 7: WQE Buffer Requirements                                              |    |

| Table 8: PKO Command Buffers Overview                                         |    |

| Table 9: PKO Command Buffers Requirements                                     |    |

| Table 10: Pool Information Functions                                          |    |

| Table 11: Easy-to-Use Functions                                               |    |

| Table 12: Advanced FPA Functions                                              |    |

| Table 13: Basic Code Review Checklist                                         |    |

| Table 14: Defaults for Configurable Per-Pool Buffer Cache and Watermarks      |    |

| Table 15: Fixed Per-Pool Watermarks and Size (If No Configuration Registers)  |    |

| Table 16: Watermark Facts                                                     | 50 |

| Table 16:    Watermark Facts      Table 17:    Status and Debugging Registers | 55 |

| Table 18: Advanced Initialization Registers.                                  |    |

| Table 19: Performance Tuning Checklist                                        | 63 |

| Table 20: Advanced Code Review Checklist                                      |    |

| Table 21: FPA Registers used in Buffer Allocate and Free Operations           |    |

| Table 22: FPA Register Summary                                                | 67 |

| Table 23: FPA Key Register Field Summary                                      | 68 |

| Table 24: DFA Unit                                                            | 70 |

| Table 25: IPD Unit                                                            | 70 |

| Table 26: PCI/PCIe DMA Engine                                                 | 70 |

| Table 27: PKO Unit                                                            | 71 |

| Table 28: RAID Unit                                                           |    |

| Table 29: TIMER Unit                                                          |    |

| Table 30: ZIP Unit                                                            | 72 |

|                                                                               |    |

## LIST OF FIGURES

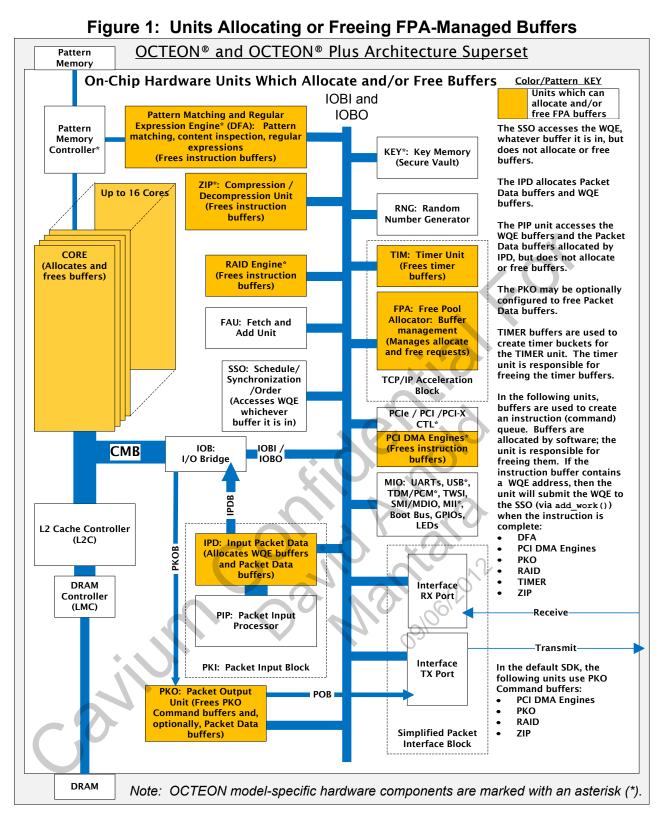

| Figure 1: Units Allocating or Freeing FPA-Managed Buffers              | 8  |

|------------------------------------------------------------------------|----|

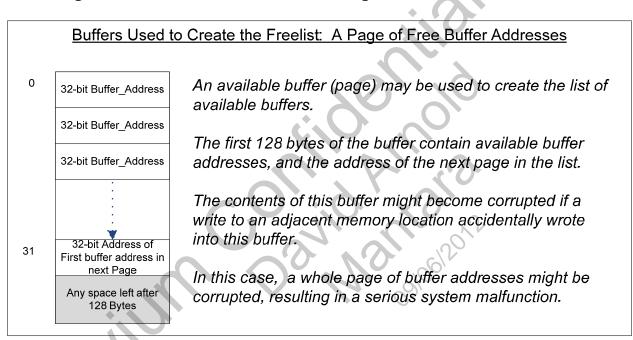

| Figure 2: A Free Buffer used as a Page of Free Buffer Addresses        | 44 |

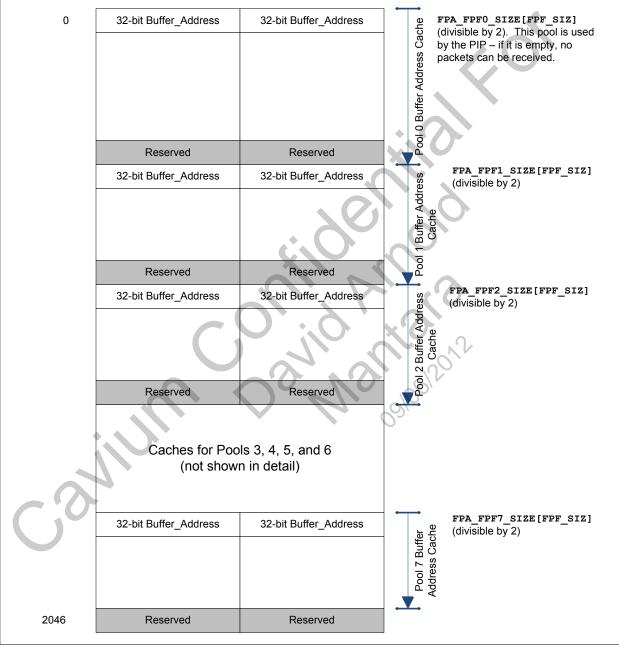

| Figure 3: FPA In-Unit Buffer Address Cache – Simplified Internal View  | 47 |

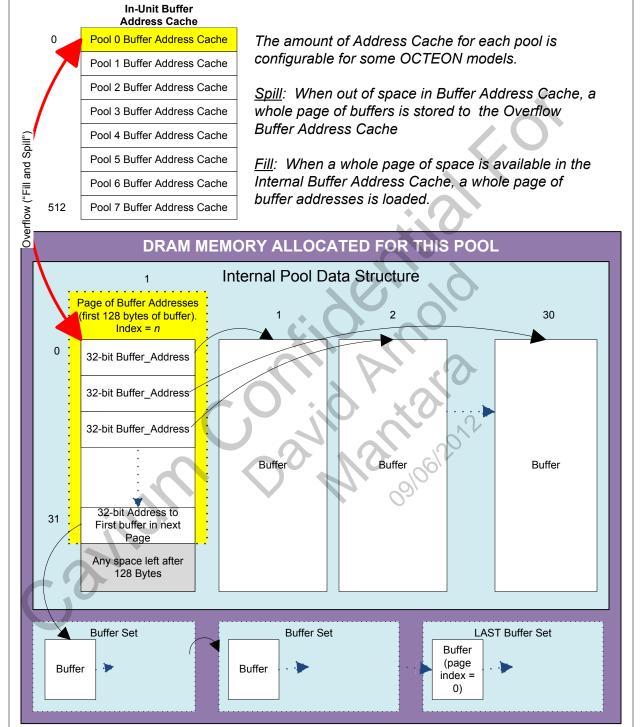

| Figure 4: FPA Buffer Pool: Simplified Internal View                    | 48 |

| Figure 5: FPA Read Watermark: Simplified Internal View                 | 51 |

| Figure 6: FPA Write Watermark – Simplified Internal View               | 52 |

| Figure 7: Overwriting Memory: Buffer Not Cache Line Size Aligned       | 56 |

| Figure 8: Overwriting Memory: Buffer not a Multiple of Cache Line Size | 57 |

| Figure 9: DWB and Why Buffers Need to be a Multiple of Cache Line Size | 58 |

| Figure 10: Buffer Freed to the Wrong Pool                              | 59 |

| Figure 11: Buffer Accidentally Freed More Than Once                    | 60 |

,.-,.-010612012 , x

## 1 Introduction

This chapter provides details about the Free Pool Allocator (FPA) unit. The FPA manages pools of pre-allocated memory buffers, for example Packet Data buffers or WQE buffers. Software running on the cores and also some hardware units may allocate and free buffers from/to the FPA pools.

Everyone who is writing or debugging code running on OCTEON processors should read this chapter, although some material toward the end is targeted to readers who are adding to the Simple Executive API or writing a custom API.

Before reading this chapter, please read the *OCTEON Programmer's Guide, Volume 1* and the *Configuration* and *Advanced Topics* chapters before reading this chapter. The *Configuration* chapter provides basic information on how to configure the FPA pools, but additional information is provided here.

This chapter provides:

- Configuration information

- Details on easy-to-use API data structures and functions

- Basic code review checklist

- Details on advanced API functions

- Debugging information

- Performance tuning information

Note that a downloadable simple example (fpa\_simplified) of using the FPA API is provided at the Cavium Networks Technical Support Site in the same directory where an electronic copy of this chapter may be found. The downloadable file is a tar file. Untar it into the examples directory of the SDK. To build and run the example, follow the directions in the README.txt file provided with the example.

Note that the fpa\_simplified example code only shows the FPA API, and is not useful for doing any actual work. The passthrough example code supplied with the SDK provides a realistic example of using the FPA to do packet processing.

Other example code can be found in the examples directory, in the SDK.

## 2 Overview of FPA

#### 2.1 Functional Overview

As described in the *Packet Flow* chapter, the FPA supplies hardware units with Packet Data buffers, Work Queue Entry (WQE) buffers, and PKO Command buffers (the three pools essential for packet processing). All applications performing packet I/O will require these three types of buffers. The FPA may also supply buffers for TIM, DFA, RAID, PCI DMA Engines, and ZIP hardware units as well as user-defined buffers for use by the cores. (Note that the code supplied in the SDK configures PCI DMA Engines, RAID, and ZIP units to use the PKO Command buffers. Each of these engines frees the PKO Command buffer back to the FPA after it has been used.)

Hardware acceleration includes some buffer allocation and free by hardware units. For example, PIP/IPD and PKO both make use of FPA Pool 0 in order to support high-speed packet I/O without burdening the cores with a lot of buffer management overhead. PIP/IPD automatically allocates available Packet Data buffers from FPA pool 0 to contain new ingress packets, and the PKO can optionally free Packet Data buffers back to FPA pool 0 after it egresses the content of the Packet Data buffer.

On startup, the application enables the FPA, and then populates the FPA pools by allocating memory for each type of buffer (such as Packet Data buffer or Work Queue Entry buffer) and freeing the buffers to the FPA to create buffer pools for subsequent use. The FPA manages these pre-allocated buffer pools.

Once the FPA and associated hardware units are correctly initialized, use of FPA-managed buffers is efficient, easy and convenient.

#### 2.2 Hardware Blocks Which Use FPA-Managed Buffers

In the figure below the blocks highlighted in yellow are hardware units, including the cores, which allocate, use, and/or free FPA-managed buffers.

FPA-managed buffers are used by almost every unit in the OCTEON processor:

CN OCTEON PRG GUIDE Vol2A

Cavium Networks Proprietary and Confidential - DO NOT COPY

5-8

| Table 1: Units Allocating/Freein | a Ruffer Addresses  | or Accessing Buffers |

|----------------------------------|---------------------|----------------------|

| Table 1. Units Anocating/Freem   | y Dullel Adulesses, | OF ACCESSING DUNERS  |

| Unit                                                                                | Populate<br>Pools | Manage<br>Allocate<br>and Free<br>Requests | Allocate<br>Buffer                                 | Free Buffer                                                        | Access Buffer                                           | Submit<br>WQE to<br>SSO |

|-------------------------------------------------------------------------------------|-------------------|--------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|-------------------------|

| Cores<br>(via<br>software)                                                          | Yes               | No                                         | Yes                                                | Yes                                                                | Yes - all buffers                                       | Yes                     |

| DFA                                                                                 | No                | No                                         | No                                                 | Yes - Note1                                                        | Yes - See Note3                                         | Yes -<br>Note2          |

| FPA                                                                                 | No                | Yes                                        | No                                                 | No                                                                 | Yes - all buffers                                       | No                      |

| IPD                                                                                 | No                | No                                         | Yes - Packet<br>Data Buffers<br>and WQE<br>buffers | No                                                                 | Yes - Packet Data<br>buffers and WQE<br>buffers         | Yes                     |

| PCI<br>DMA<br>Engines                                                               | No                | No                                         | No                                                 | Yes - Note1                                                        | Yes - See Note3                                         | Yes -<br>Note2          |

| РКО                                                                                 | No                | No                                         | No                                                 | Yes - PKO Command<br>buffers and optionally<br>Packet Data buffers | Yes - PKO Command<br>buffers and Packet<br>Data buffers | No                      |

| RAID<br>Engine                                                                      | No                | No                                         | No                                                 | Yes - Note1                                                        | Yes - See Note3                                         | Yes -<br>Note2          |

| SSO                                                                                 | No                | No                                         | No                                                 | No                                                                 | Yes - WQE Buffers                                       | N/A                     |

| TIM                                                                                 | No                | No                                         | No                                                 | Yes - Note1                                                        | Yes - See Note3                                         | Yes -<br>Note2          |

| ZIP                                                                                 | No                | No                                         | No                                                 | Yes - Note1                                                        | Yes - See Note3                                         | Yes -<br>Note2          |

| Notes                                                                               |                   |                                            |                                                    |                                                                    |                                                         |                         |

| Note1: Frees the Instruction buffer when all instructions in it have been processed |                   |                                            |                                                    |                                                                    |                                                         |                         |

|                                                                                     |                   |                                            |                                                    | the SSO to be scheduled                                            | to a core.                                              |                         |

| Note3: This unit accesses the instruction buffer                                    |                   |                                            |                                                    |                                                                    |                                                         |                         |

This is why correct FPA configuration and careful use of FPA-managed buffers are essential to a healthy system. If something goes wrong with the FPA-managed buffers, the entire system may be affected, including errors which can be very distant from the original problem, and therefore very tricky to debug.

Despite the large number of units using the FPA-managed buffers, only a few buffer pools are needed:

- Packet Data buffers

- WQE buffers

- PKO Command buffers (in the default SDK, these are used by the PCI DMA Engines, PKO, RAID, and ZIP units)

- TIMER buffers

- DFA buffers

Hardware units which automatically allocate, use, and free buffers from the FPA must be correctly initialized. Incorrect hardware unit initialization can result in:

- over-writing buffers (For example, if the *mbuf* size provided to the IPD is incorrectly set to larger than the amount of available space in the Packet Data buffer, then the IPD will overwrite adjacent memory at the end of the buffer. The term *mbuf* stands for memory buffer. See the *Glossary* for more information.)

- allocating buffers from the wrong pool

- freeing buffers to the wrong pool

For these reasons, care must be taken when initializing the hardware units.

More information on hardware unit initialization is provided in Section 3 – "General Pool Configuration and Population Information".

#### 2.3 Operations

The FPA supports three operations:

- **buffer\_allocate (synchronous)**: The core waits until the address of an available buffer is returned (or NULL if no buffers are available)

- **buffer\_allocate (asynchronous)**: The core does not wait for the buffer address to be returned. At a later time, the core retrieves the address from the specified scratchpad area.

- **buffer\_free (synchronous)**: This operation returns the specified buffer address to the specified pool.

Either the cores or some of the hardware units can perform these operations.

These operations are discussed in detail in the Configuration and Advanced Topics chapters.

#### 2.4 FPA Registers

The FPA registers may be used to customize the FPA configuration and retrieve status information. For instance, the register FPA\_QUEn\_AVAILABLE has a field QUE\_SIZ which contains the number of available buffers in the specified pool ("*n*" is a number [0-7] which specifies the pool, as in FPA\_QUE2\_AVAILABLE.) (The register/field combination is written: FPA\_QUEN\_AVAILABLE[QUE\_SIZ].)

When customizing the SDK by accessing registers, use the API provides functions to read and write the registers safely and conveniently:

- cvmx\_read\_csr()

- cvmx\_write\_csr()

Race conditions which may otherwise occur are discussed in the *Configuration* and *Advanced Topics* chapters.

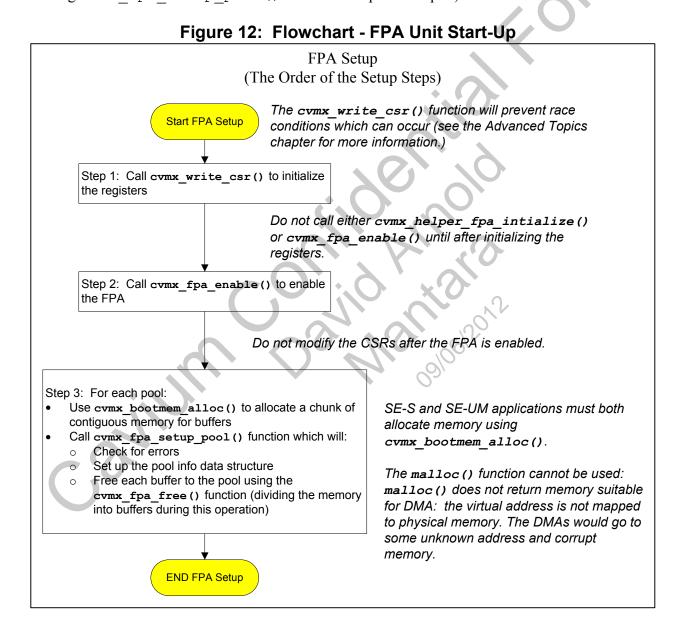

*Note:* Do not modify these registers after the FPA is enabled. See Figure 12 – *"Flowchart - FPA "*.

#### 2.5 Using the FPA

Before the FPA can be used, it must be:

- 1. Configured

- 2. Initialized

- 3. Enabled

- 4. Pools must be populated with buffers

These concepts were introduced in the *Configuration* chapter. This section provides FPA-specific information. Functions mentioned in this section are discussed in more detail in Section 7 – "Simple Executive API".

#### 2.5.1 Configure the FPA Unit

Simple Executive configuration is done at build time. See Section 3 – "General Pool Configuration and Population Information" for FPA-specific configuration information. See the *Configuration* chapter for more information.

#### 2.5.2 Initialize the FPA Unit

Unit initialization is done at runtime. The Simple Executive API will manage any basic initialization items. Advanced initialization items are covered in the Advanced Section of this chapter, which begins with Section 11.3 – "Initializing the Per-Pool Address Cache Allotment or Watermarks".

#### 2.5.3 Enable the FPA Unit

Unit enable is done at runtime. The FPA hardware unit is enabled via either the fpa\_enable() function or cvmx\_helper\_initialize\_fpa() (which calls the fpa\_enable() function. The FPA must be enabled before the pools are populated, or runtime errors will occur (such as an incorrect available buffer count).

#### 2.5.4 Populate the FPA Pools

Pool population is done at runtime. For easy pool population, see Section 7.3.2.1 – "Example Code: cvmx\_helper\_initialize\_fpa()", for advanced pool population, see Section 7.4.1.2 – "Example Code: Calling cvmx\_fpa\_setup\_pool()".

See Section 3.2.4 – "Can More Buffers be Added to a Buffer Pool at Any Time?" for more information.

#### 2.5.4.1 Allocating Memory for FPA-Managed Buffers

If the Cavium Networks Ethernet driver is used with the application, then the Ethernet driver is responsible for allocating memory for the Packet Data buffers, WQE buffers, and PKO Command buffers.

Both SE-S and SE-UM applications must allocate memory for FPA-managed buffers using cvmx\_bootmem\_alloc(). This function will return memory which is suitable for DMA operations.

The Linux function malloc() cannot be used: malloc() does not return memory suitable for DMA: the virtual address is not mapped to physical memory. The DMAs would go to some unknown address and corrupt memory.

## **3** General Pool Configuration and Population Information

The *Configuration* chapter provides information on how to configure FPA pools and scratchpad areas. This section provides guidelines for making configuration and population (buffer count) choices for the three FPA pools essential for packet processing:

- Packet Data buffer pool

- Work Queue Entry buffer pool (Note that some OCTEON models can store the WQE data structure in the Packet Data buffer. If this feature is used, the WQE buffers are not needed for packet processing.)

- PKO Command buffer pool

The default SDK uses PKO Command buffers for the following hardware unit's instruction queues. This reduces the number of FPA pools needed:

- PCI DMA Engines

- PKO

- RAID

- ZIP

### 3.1 Default Simple Executive Pool and Scratchpad Area Configuration

The following table shows the default Simple Executive pool and scratchpad area configuration. In the default Simple Executive, PCI DMA Engines, PKO, RAID, and ZIP all use the PKO Command buffers pool. Separate pools can be configured for these uses if required.

| DFA Buffers Pool (ifdef CVMX ENABLE DFA FUNCTIONS)         |                                   |  |

|------------------------------------------------------------|-----------------------------------|--|

|                                                            |                                   |  |

| Name                                                       | CVMX_FPA_DFA_POOL                 |  |

| Descriptive String                                         | "DFA command buffers"             |  |

| Pool Number (Default value)                                | 4                                 |  |

| Buffer Size (Default value)                                | 2 * cache line size (256 bytes)   |  |

| Protected / Permanent                                      | Yes                               |  |

| Packet Data Buffers Pool (if                               | def CVMX_ENABLE_PKO_FUNCTIONS)    |  |

| Name                                                       | CVMX_FPA_PACKET_POOL              |  |

| Descriptive String                                         | "Packet buffers"                  |  |

| Pool Number (Default value)                                | 0 (cannot be changed)             |  |

| Buffer Size (Default value)                                | 16 * cache line size (2048 bytes) |  |

| Protected / Permanent                                      | Yes                               |  |

| PKO Command Buffers Pool (ifdef CVMX_ENABLE_PKO_FUNCTIONS) |                                   |  |

| Name                                                       | CVMX_FPA_OUTPUT_BUFFER_POOL       |  |

| Descriptive String                                         | "PKO queue command buffers"       |  |

| Pool Number (Default value)                                | 2                                 |  |

#### Table 2: Default Simple Executive Pool Configuration

| Buffer Size (Default value) | 8 * cache line size (1024 bytes)          |

|-----------------------------|-------------------------------------------|

| Protected / Permanent       | Yes                                       |

| Timer Buffers Pool (ifdef   | CVMX_ENABLE_TIMER_FUNCTIONS)              |

| Name                        | CVMX_FPA_TIMER_POOL                       |

| Descriptive String          | "TIM command buffers"                     |

| Pool Number (Default value) | 3                                         |

| Buffer Size (Default value) | 8 * cache line size (1024 bytes)          |

| Protected / Permanent       | Yes                                       |

| Work Queue Entry Buffers    | Pool (ifdef CVMX_ENABLE_HELPER_FUNCTIONS) |

| Name                        | CVMX_FPA_WQE_POOL                         |

| Descriptive String          | "Work queue entries"                      |

| Pool Number (Default value) | 1                                         |

| Buffer Size (Default value) | 1 * cache line size (128 bytes)           |

| Protected / Permanent       | Yes                                       |

#### Table 3: Default Simple Executive Scratchpad Configuration

| Scratchpad 1 - generic - used for cvmx_fpa_async_alloc() (ifdef<br>CVMX_ENABLE_PKO_FUNCTIONS) |                               |  |

|-----------------------------------------------------------------------------------------------|-------------------------------|--|

| Name                                                                                          | CVMX_SCR_SCRATCH              |  |

| Descriptive String                                                                            | "Generic scratch iobdma area" |  |

| Size (Default value)                                                                          | 8 bytes                       |  |

| Protected / Permanent                                                                         | No                            |  |

#### 3.2 Configuration Overview

#### 3.2.1 Rules