# Reference Manual

WANic-58xx Packet Processor Sixth Edition

Part No: 87002020-820

# **Table of Contents**

| ' ' | reface                                                                                                                                                                                                                                                                                                                                                   | 11                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1   | • Overview                                                                                                                                                                                                                                                                                                                                               | 15                                                 |

|     | 1.1 Features.                                                                                                                                                                                                                                                                                                                                            | 15                                                 |

|     | 1.2 Product Overview.                                                                                                                                                                                                                                                                                                                                    |                                                    |

|     | 1.3 Hardware Overview.                                                                                                                                                                                                                                                                                                                                   | 16                                                 |

|     | 1.4 Software Overview.                                                                                                                                                                                                                                                                                                                                   | 17                                                 |

|     | 1.4.1 Software Components                                                                                                                                                                                                                                                                                                                                | 17                                                 |

|     | 1.4.2 Additional Software                                                                                                                                                                                                                                                                                                                                | 17                                                 |

|     | 1.4.3 Operating System Support                                                                                                                                                                                                                                                                                                                           | 17                                                 |

|     | 1.4.4 Cavium Networks Users' Organization Web Site                                                                                                                                                                                                                                                                                                       | 18                                                 |

|     | 1.5 Specification.                                                                                                                                                                                                                                                                                                                                       | 19                                                 |

|     | 1.6 Emission Compliance Notice.                                                                                                                                                                                                                                                                                                                          | 20                                                 |

|     | 1.7 RoHS and WEEE Compliance                                                                                                                                                                                                                                                                                                                             | 20                                                 |

|     | 1.8 Warranty and Repair.                                                                                                                                                                                                                                                                                                                                 | 21                                                 |

|     | 1.8.1 Warranty                                                                                                                                                                                                                                                                                                                                           | 21                                                 |

|     | 1.8.2 Customer Technical Support                                                                                                                                                                                                                                                                                                                         | 21                                                 |

|     | 1.9 Handling Precautions                                                                                                                                                                                                                                                                                                                                 | 22                                                 |

|     | 1.9.1 ESD Precautions                                                                                                                                                                                                                                                                                                                                    | 22                                                 |

|     | 1.9.2 Optical/Laser Safety Notices                                                                                                                                                                                                                                                                                                                       | 22                                                 |

| 2   | Hardware Description                                                                                                                                                                                                                                                                                                                                     | 25                                                 |

|     | 2.1 Hardware Components.                                                                                                                                                                                                                                                                                                                                 | 25                                                 |

|     |                                                                                                                                                                                                                                                                                                                                                          |                                                    |

|     | 2.2 Multi-Core Processor.                                                                                                                                                                                                                                                                                                                                |                                                    |

|     | 2.2 Multi-Core Processor.  2.2.1 Multi-Core Processor Interfaces                                                                                                                                                                                                                                                                                         | 26                                                 |

|     | 2.2 Multi-Core Processor.  2.2.1 Multi-Core Processor Interfaces  2.2.2 Multi-Core Processor Boot Bus                                                                                                                                                                                                                                                    | 26                                                 |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus                                                                                                                                                                                                                                                                                | 26                                                 |

|     | 2.2.1 Multi-Core Processor Interfaces                                                                                                                                                                                                                                                                                                                    | 26                                                 |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface.                                                                                                                                                                                                                                                       | 26                                                 |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA.                                                                                                                                                                                                                                             | 2627293031                                         |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory.                                                                                                                                                                                                                                 | 2627293031                                         |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM                                                                                                                                                                                                                | 26<br>27<br>29<br>30<br>31                         |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM 2.5.2 Optional RLDRAM II                                                                                                                                                                                       | 26<br>27<br>29<br>30<br>31<br>31                   |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM 2.5.2 Optional RLDRAM II 2.5.3 Flash                                                                                                                                                                           | 26<br>27<br>29<br>31<br>31<br>31                   |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM 2.5.2 Optional RLDRAM II 2.5.3 Flash 2.5.4 Serial EEPROM                                                                                                                                                       | 26<br>27<br>29<br>31<br>31<br>31<br>32<br>32       |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM 2.5.2 Optional RLDRAM II 2.5.3 Flash 2.5.4 Serial EEPROM 2.6 Gigabit Ethernet PHY Devices.                                                                                                                     | 26293031313232                                     |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus  2.3 PCI/PCI-X Interface.  2.4 FPGA.  2.5 Memory.  2.5.1 DDR2 SDRAM  2.5.2 Optional RLDRAM II  2.5.3 Flash  2.5.4 Serial EEPROM  2.6 Gigabit Ethernet PHY Devices.  2.7 SFP Front Panel Connectors.                                                                            | 26<br>27<br>29<br>31<br>31<br>31<br>32<br>33<br>33 |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM 2.5.2 Optional RLDRAM II 2.5.3 Flash 2.5.4 Serial EEPROM 2.6 Gigabit Ethernet PHY Devices. 2.7 SFP Front Panel Connectors. 2.8 Dual In-Line Package (DIP) Switches.                                            | 262930313132333334                                 |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM 2.5.2 Optional RLDRAM II 2.5.3 Flash 2.5.4 Serial EEPROM 2.6 Gigabit Ethernet PHY Devices. 2.7 SFP Front Panel Connectors. 2.8 Dual In-Line Package (DIP) Switches. 2.8.1 S1 DIP Switch                        | 26272931313132333434                               |

|     | 2.2.1 Multi-Core Processor Interfaces 2.2.2 Multi-Core Processor Boot Bus 2.3 PCI/PCI-X Interface. 2.4 FPGA. 2.5 Memory. 2.5.1 DDR2 SDRAM. 2.5.2 Optional RLDRAM II 2.5.3 Flash. 2.5.4 Serial EEPROM. 2.6 Gigabit Ethernet PHY Devices. 2.7 SFP Front Panel Connectors. 2.8 Dual In-Line Package (DIP) Switches. 2.8.1 S1 DIP Switch 2.8.2 S2 DIP Switch | 2627293031313233343435                             |

|            | 2.10.2 SFP Modules                           | 39    |

|------------|----------------------------------------------|-------|

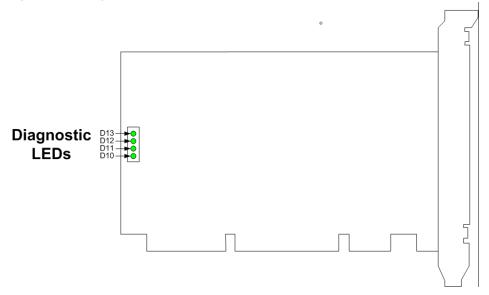

|            | 2.11 Diagnostic LEDs                         | . 40  |

|            | 2.12 Headers                                 | 40    |

|            | 2.12.1 JTAG Scan Chain                       | 40    |

|            | 2.12.2 Enhanced JTAG                         | 41    |

|            | 2.12.3 RS-232 Serial Port                    | 42    |

|            | 2.13 Temperature Monitor.                    | . 44  |

|            | 2.14 Power and Cooling.                      | 45    |

|            | 2.14.1 Power Supplies                        | 45    |

|            | 2.14.2 Thermal Management                    | 45    |

| 3          | • FPGA Registers                             | . 47  |

|            | 3.1 FPGA General Registers                   | 48    |

|            | 3.2 I2C Registers                            |       |

|            | 3.2.1 Writing Data                           |       |

|            | 3.2.2 Reading Data                           | 58    |

| <b>/</b> ı | • Coftware Features                          | 67    |

| 4          | • Software Features                          |       |

|            | 4.1 Overview.                                |       |

|            | 4.2 Cavium Software Development Kit.         |       |

|            | 4.2.1 Cavium Ethernet Driver                 |       |

|            | 4.2.2 Embedded File System                   |       |

|            | 4.2.3 Simple Exec Library                    |       |

|            | 4.3 User Application.4.4 U-Boot Bootloader.  |       |

|            | 4.4.1 UART Command Interface                 |       |

|            | 4.4.2 Building U-Boot                        |       |

|            | 4.4.3 Boot Progress Status Messages          |       |

|            | 4.4.4 IP Configuration Acquisition with DHCP |       |

|            | 4.4.5 U-Boot Scripting                       |       |

|            | 4.4.6 Environment Variables                  |       |

|            | 4.4.7 Automated UA Executable Load and Boot  |       |

|            | 4.4.8 U-Boot Error Handling                  |       |

|            | 4.4.9 U-Boot Commands                        |       |

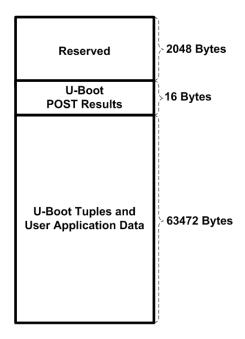

|            | 4.5 EEPROM                                   |       |

|            | 4.5.1 EEPROM Mapping                         |       |

|            | 4.5.2 EEPROM Tuples                          |       |

|            | 4.5.3 EEPROM Tuple Update and Enumeration    |       |

|            | 4.5.4 Tuple Format                           |       |

|            | 4.6 Linux Support Package (LSP).             |       |

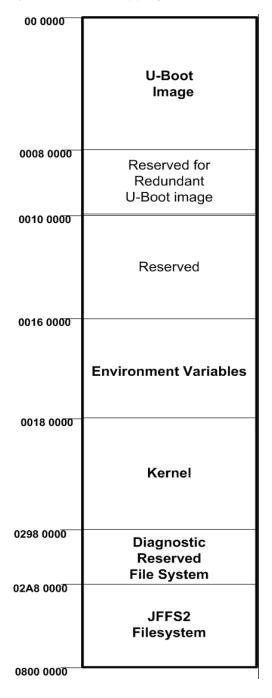

|            | 4.6.1 Flash Driver                           |       |

|            | 4.7 NPA Driver                               | . 101 |

|            | 4.7.1 Linux /proc/ File System               | . 101 |

|            | 4.7.2 IOCTL Device interface                 | . 102 |

|            | 4.7.3 IOCTL Commands                         | . 103 |

| 4.7.4 Proc File Updates 4.7.5 Exported Kernel Symbols 4.8 Examples. 4.8.1 Linux Applications Examples 4.8.2 Simple Exec Application Examples                                                                                                                                                                                                                                                          | 107<br>108<br>108                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 5 • WANic-58xx Diagnostic Utility  5.1 Overview.  5.1.1 Setup  5.1.2 Running the Diagnostic Utility                                                                                                                                                                                                                                                                                                   | 113                                                  |

| A • Hardware Installation and Removal Procedures  A.1 Installation Precautions A.2 Installation Overview A.3 Mini-RDIMM Installation and Removal A.3.1 Mini-RDIMM Installation A.3.2 Mini-RDIMM Removal A.4 WANic-58xx Installation and Removal A.4.1 WANic-58xx Installation A.4.2 WANic-58xx Removal A.5 SFP Module installation and Removal A.5.1 SFP Module Installation A.5.2 SFP Module Removal | 129<br>130<br>130<br>131<br>131<br>133<br>134<br>135 |

| B • GNU General Public License                                                                                                                                                                                                                                                                                                                                                                        | 137                                                  |

| C • GE INTELLIGENT PLATFORMS, INC. Software License Agreement – Object C                                                                                                                                                                                                                                                                                                                              | ode 143                                              |

| D • GE INTELLIGENT PLATFORMS, INC. Software License Description                                                                                                                                                                                                                                                                                                                                       |                                                      |

| Glossary                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |

| IIIUでん                                                                                                                                                                                                                                                                                                                                                                                                | <u></u>                                              |

# **List of Figures**

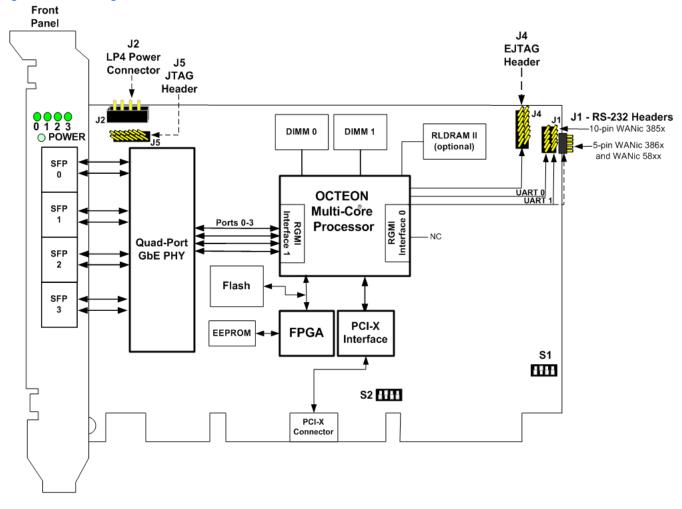

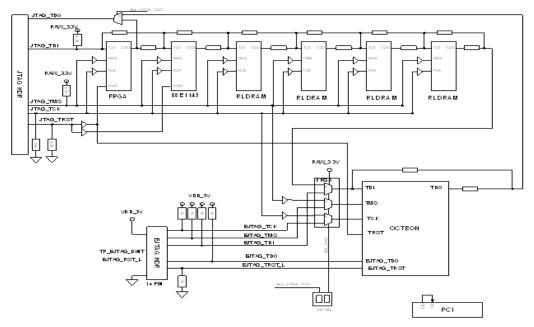

| Figure 2-1 Block Diagram                                    | 26  |

|-------------------------------------------------------------|-----|

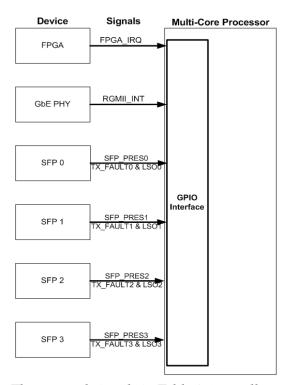

| Figure 2-2 GPIO Interface to SFPs                           | 28  |

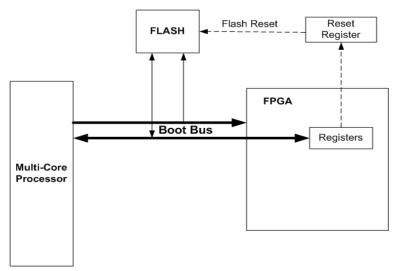

| Figure 2-3 Flash Connection to Boot Bus                     | 32  |

| Figure 2-4 DIP Switches                                     | 35  |

| Figure 2-5 Reference Clock Circuitry                        | 37  |

| Figure 2-6 Front Panel LEDs                                 | 38  |

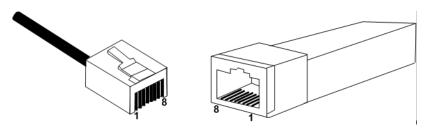

| Figure 2-7 RJ-45 Connector                                  | 39  |

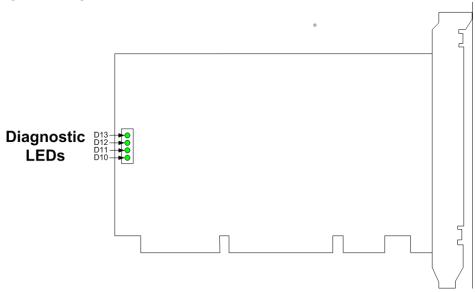

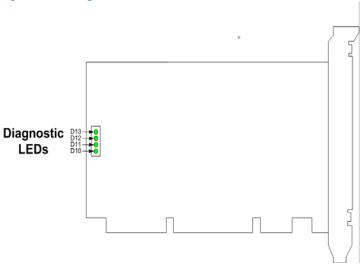

| Figure 2-8 Diagnostic LEDs                                  | 40  |

| Figure 2-9 JTAG Scan Chain and EJTAG Interface              | 41  |

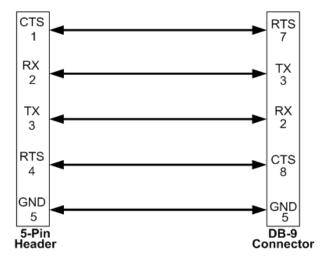

| Figure 2-10 Serial Cable Pinout                             | 43  |

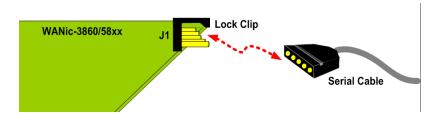

| Figure 2-11 Serial Cable Connection                         | 43  |

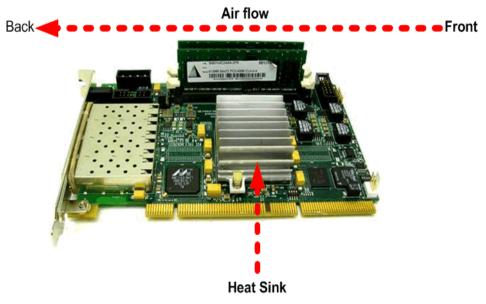

| Figure 2-12 Air Flow on the WANic-58xx                      | 46  |

| Figure 3-1 FPGA Revision Register @ Base + 00h              | 49  |

| Figure 3-2 Board ID and DIP Switch Register @ Base + 01h    | 50  |

| Figure 3-3 LED Control Register @ Base + 02h                | 51  |

| Figure 3-4 Diagnostic LEDs                                  | 51  |

| Figure 3-5 Interrupt Control Register @ Base + 03h          | 52  |

| Figure 3-6 Interrupt Status Register @ Base + 04h           | 53  |

| Figure 3-7 Peripheral Reset Register @ Base + 05h           | 54  |

| Figure 3-8 Transmit Control Register @ Base + 06h           | 55  |

| Figure 3-9 Fan and Temperature Register @ Base + 07h        | 56  |

| Figure 3-10 I2C Control Register @ Base + Address           | 59  |

| Figure 3-11 I2C Address Low Register @ Base + Low Address   | 60  |

| Figure 3-12 I2C Address High Register @ Base + High Address | 60  |

| Figure 3-13 I2C Data Register @ Base + Address              | 61  |

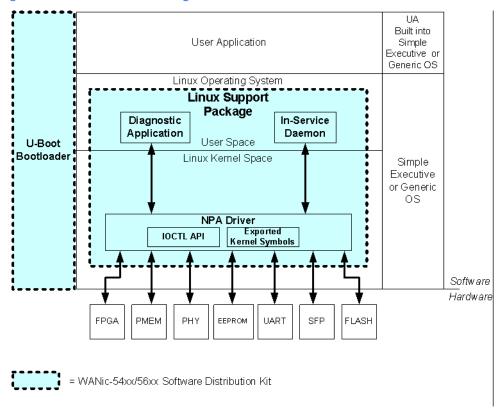

| Figure 4-1 Software Block Diagram                           | 64  |

| Figure 4-2 S2 DIP Switch Bank                               | 69  |

| Figure 4-3 EEPROM Mapping                                   | 78  |

| Figure 4-4 Flash Mapping                                    | 97  |

| Figure 4-5 IOCTL Commands and Structures                    | 102 |

| Figure 4-6 IOCTL Command Types                              | 105 |

| Figure 4-7 Exported Kernel Symbols.                         | 107 |

| Figure 5-1 Command Line Options                             | 114 |

| Figure 5-2 Diagnostic Utility Main Menu                     | 116 |

| Figure 5-3 View Test Results Display                        | 118 |

| Figure 5-4 EEPROM Menu                                      | 119 |

| Figure 5-5 Run Auto Test                                    |     |

| Figure 5-6 Test Configuration with Cable Attachment         | 121 |

| Figure 5-7 Auto Test Configuration Menu                     | 121 |

| Figure 5-8 Diagnostic LED Location                          | 123 |

| Figure 5-9 Flash Menu                                  | 124 |

|--------------------------------------------------------|-----|

| Figure 5-10 Log File Location                          | 125 |

| Figure 5-11 Show Core Temperature                      | 126 |

| Figure 5-12 Memory Test Results                        | 127 |

| Figure 5-13 Memory Test with Command Line Parameter –a | 127 |

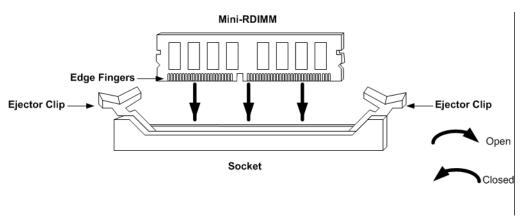

| Figure A-1 DIMM Installation                           | 130 |

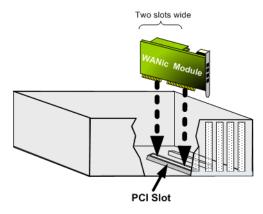

| Figure A-2 Installation in a PCI Bus Chassis           | 131 |

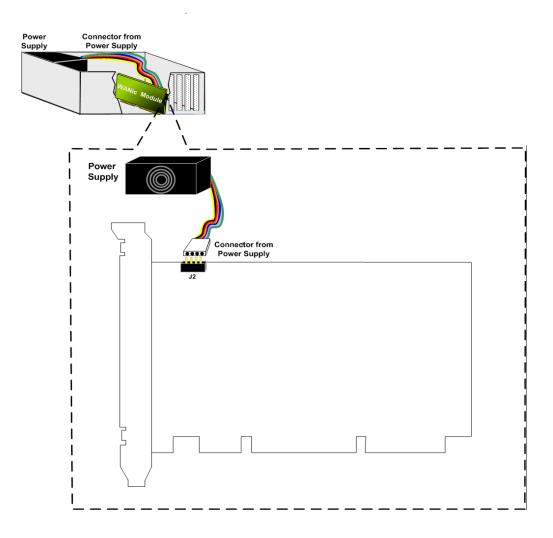

| Figure A-3 Connecting to the Power Supply              | 132 |

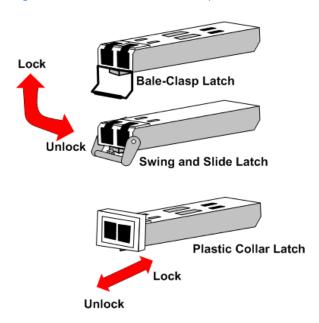

| Figure A-4 SFP Module with Clasp                       | 136 |

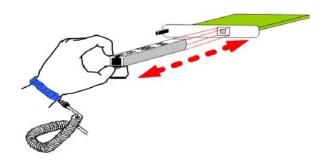

| Figure A-5 Inserting or Removing an SFP Module.        |     |

# **List of Tables**

| Table 1-1 Featured Components                         |     |

|-------------------------------------------------------|-----|

| Table 1-2 WANic-58xx Hardware Specification           | 19  |

| Table 2-1 GPIO Signal Description                     | 28  |

| Table 2-2 JTAG Mode S1 DIP Switch Configuration       |     |

| Table 2-3 Boot Mode S1 DIP Switch Configuration       | 35  |

| Table 2-4 Diagnostic Mode S1 DIP Switch Configuration | 35  |

| Table 2-5 S2 DIP Switch                               | 36  |

| Table 2-6 Board Status LEDs                           | 38  |

| Table 2-7 RJ-45 Pin Assignment                        | 39  |

| Table 2-8 UARTO Signals                               | 42  |

| Table 2-9 L4 Power Supply Pinout                      | 45  |

| Table 2-10 Current and Power Limits                   | 45  |

| Table 2-11 Thermal/Power Budget                       | 45  |

| Table 3-1 FPGA Memory Mapped Registers                |     |

| Table 4-1 Boot Progress Status Messages               | 70  |

| Table 4-2 Environment Variables                       | 73  |

| Table 4-3 Load and Boot Image Default Entries         | 74  |

| Table 4-4 POST Failures                               | 75  |

| Table 4-1 U-Boot Commands                             |     |

| Table 4-2 EEPROM Tuples                               | 79  |

| Table 4-3 Flash Driver Functions                      | 98  |

| Table 4-4 Flash Partitioning                          | 99  |

| Table 4-5 IOCTL Commands                              | 103 |

| Table 5-1 Command Line Parameters                     | 114 |

| Table 5-2 Diagnostic Utility Main Menu                | 116 |

| Table 5-3 EEPROM Menu Options                         |     |

| Table 5-4 Test Configuration Menu Options             | 122 |

| Table 5-5 Diagnostic LED Test Prompts                 | 123 |

| Table 5-6 Flash Menu Ontions                          | 124 |

#### **Preface**

This document provides technical information for the WANic-58xx Packet Processor. The WANic-58xx Packet Processors (hereafter referred to as the WANic-58xx), provide 10/100/1000 Megabits per second (Mbps) Ethernet speeds and feature a Peripheral Component Interconnect Extended (PCI-X®) 64-bit, 133 MegaHertz (MHz) control and data plane host interface.

The WANic-58xx provide four Gigabit Ethernet (GbE) ports in a flexible configuration of either copper or fiber front access through Small Form Factor Pluggable (SFP) modules. The WANic-58xx are available in a variety of configurations. (Unless specified otherwise, WANic-58xx refers to all models.)

The WANic-58xx complies with the Restriction of Hazardous Substances (RoHS) directive.

This manual only describes the WANic-58xx as the WANic-38xx is no longer sold by GE Intelligent Platforms. If you have questions about this product or any other GE Intelligent Platforms product, please contact GE Intelligent Platforms Customer Technical Support.

#### **Audience**

This manual is intended for the engineers or developers who use the WANic-58xx to develop telecommunication and data processing applications.

It is assumed that the user is familiar with standard cabling, configurations of operating systems, networks, and PCI-X technology as well as C programming with the Linux Operating System.

# **Referenced Documentation**

Documentation referenced in this manual includes the following industry and vendor documentation:

# **Industry Standard Specifications**

- IEEE 802.3–Standard for Information Technology--Telecommunications and information exchange between systems--Local and metropolitan area networks--Specific requirements--Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications, American National Standards Institute (ANSI) 2005, www.ieee.org.

- PCI-X Electrical and Mechanical Addendum to the PCI Local Bus Specification Revision 2.0a, PCI-SIG, 2003, www.pcisig.com.

- PCI Local Bus Specification Revision 3.0 PCI-SIG, 2002, www.pcisig.com.

#### **Vendor Documentation**

• Cavium Networks OCTEON CN38xx/58xx Hardware Reference Manual, Cavium Networks, www.caviumnetworks.com.

# **Manual Organization**

This manual contains the following chapters and appendices:

- "Chapter 1 Overview," presents an overview of WANic-58xx hardware and firmware as well as compliance information and warranty.

- "Chapter 2 Hardware Description," describes the hardware components on the WANic-58xx. It also includes a description of connector pinouts and Light Emitting Diodes (LEDs).

- "Chapter 3 FPGA Registers," describes the register for communications between components on the WANic-58xx.

- "Chapter 4 Software Features," provides information on how to use software components to including a boot loader and Application Programming Interfaces (APIs).

- "Chapter 5 WANic-58xx Diagnostic Utility," describes the diagnostic utility, which verifies and configures components on the WANic-58xx.

- "Appendix A Hardware Installation and Removal Procedures," describes the procedures to install or hot swap the WANic-58xx.

- "Appendix B GNU General Public License," contains a copy of the GNU General Public License.

- "Appendix C GE INTELLIGENT PLATFORMS EMBEDDED SYSTEMS, INC. and its subsidiaries COMPUTER DYNAMICS OF ILLINOIS, INC. Software License Agreement Object Code: GE Intelligent Platforms Embedded Systems Software License Agreement Object Code," contains a copy of the terms and agreements for the GE Intelligent Platforms software license agreement object code.

- Appendix D GE INTELLIGENT PLATFORMS EMBEDDED SYSTEMS, INC. Software License Description for the WANic-58xx," contains a description of the software license.

This manual also contains a glossary and an index.

### **Notation Conventions**

This manual uses the following notation conventions:

- Italics emphasizes words in text and documentation or chapter titles.

- Hexadecimal values are represented as digits followed by "h", for example 0Ch.

- Courier text identifies text that the user must enter or text that displays on the screen.

For example,

Use the ioctl DevShow command to verify the driver installation.

• Bold Palatino Linotype text identifies register names.

For example,

An independent **Interrupt Control Register** is available for each I/O bus space.

• **Bold Courier text** identifies text in an example that the user must enter.

For example,

Load the driver manually using the modprob command:

#modprob -v xxxx

• Notes, cautions, and warnings call attention to essential information:

A Note calls attention to important information, such as tips and advice.

#### **CAUTION**

A Caution alerts you to conditions that could damage a device, system, or data.

#### WARNING

A Warning calls attention to actions that can cause risk of personal injury.

- Specific term definitions, as applied in this manual include:

- "May" means that there is flexibility that does not affect the outcome or result of the action.

- "Should" means that the user has flexibility but it is strongly recommended to perform the specified action to achieve an optimal outcome or result.

- "Must" means that there is no flexibility and the user is required to perform the action to achieve an optimal outcome or result.

## 1 • Overview

This chapter provides an overview of the WANic-58xx hardware and software. The high-bandwidth and high-speed PCI-X interface on the WANic-58xx is designed for optimized implementation in a wide range of compatible platforms. The WANic-58xx complies with the PCI Local Bus Specification Revision 3.0 as a dual-slot, short card.

#### 1.1 Features

The WANic-58xx features the components in Table 1-1 in several configurations:

Table 1-1 Featured Components

| Featured Component                                                       | WANic-58xx    |

|--------------------------------------------------------------------------|---------------|

| Cavium <sup>TM</sup> OCTEON <sup>TM</sup> Multi-Core Processor           | 600 MHz       |

| Service Communications Protocol (SCP) with cnMIPS64 <sup>1</sup> cores   | None          |

| Network Service Processor (NSP) or SCP with cnMIPS64 <sup>TM</sup> cores | cn5860-NSP 16 |

| Double Data Rate Type 2 (DDR2) packet memory                             | 2 GB          |

| Flash Read Only Memory (ROM)                                             | 128 MB        |

| Optional, Reduced Latency DRAM II (RLDRAM II)                            | 256 MB        |

| Front Panel I/O Gigabit Ethernet (GbE) ports                             | 4             |

| Small Form Pluggable (SFP) Transceivers                                  | 0 to 3        |

| Linux 2.6.x Operating System                                             | Supported     |

<sup>1.</sup> cnMIPS64 is the Cavium implementation of MIPS64 by MIPS Technology Inc.

Additional featured components include:

- Light Emitting diodes (LEDs) for link status and activity indication

- Field Programmable Gate Array (FPGA) as an interface to various on-board components

- PCI/PCI-X interface for Control and Data Plane operations

#### 1.2 Product Overview

The WANic-58xx is a fully-integrated packet processor that provide flexible processing capabilities for development of telecommunications and other packet processing intensive applications. The WANic-58xx is a network interface board with GbE serial links that provide the main Data Plane traffic connection. The WANic-58xx integrate a PCI-X interface to provide access to the 64-bit,133-MHz local bus for the main Control and Data Plane connection.

The WANic-58xx is available with four factory-installed front panel GbE I/O ports. Optionally, these front panel I/O ports can be configured at the factory for 10/100/1000Base-T or 1000Base-SX transmissions through the use of appropriate copper or fiber SFP modules.

#### 1.3 Hardware Overview

The WANic-58xx uses the OCTEON Multi-Core Processor technology for extensive logic integration and flexibility. The OCTEON Multi-Core Processor scales up to 600 MHz on select models, and provides an interface to powerful DDR2 SDRAM with Error Correction Code (ECC). On select models, DDR2 SDRAM provides up to 2 GB of main memory and is available with up to 16 cnMIPS cores.

The WANic-58xx is available with four front panel Ethernet I/O ports configured at the factory. The four front panel GbE ports implement the 10/100/1000Base-T and 1000Base-SX interfaces, which are defined by the IEEE 802.3 (Gigabit Ethernet) specification.

RLDRAM memory (for the Multi-Core Processor) provides fast random access with extremely high bandwidth and high density for latency-sensitive tasks. RLDRAM is optional on all WANic-58xx models.

Flash ROM provides 128 MB of memory for boot and application code storage.

The 64 KiloByte (KB) serial EEPROM on the WANic-58xx contains board-specific non-volatile data information for storage and retrieval.

FPGA registers provide the Multi-Core Processor and PCI-X host with real-time access to on-board devices. Status and control of some devices are indirectly accessed through Inter-Integrated Circuit (I2C) interfaces, which the FPGA provides.

#### 1.4 Software Overview

The WANic-58xx Software Developer's Kit (SDK) provides an easy-to-use development interface for the Linux Operating System. The WANic-58xx provides boot-up services, diagnostics, and device drivers, as well as a customized Application Programming Interface (API) for select on-board devices.

## 1.4.1 Software Components

Software for the WANic-58xx consists of the following components as described in "Chapter 4 • Software Features."

- U-Boot Bootloader loads and boots the WANic-58xx firmware.

- Linux Support Package (LSP) provides a suite of functions to access and to use the WANic-58xx hardware.

- Linux Operating System contains the Debian<sup>TM</sup> distribution with OCTEON Multi-Core Processor support.

Contact your GE Intelligent Platforms sales representative for additional operating system support.

• Diagnostic Utility – configures and exercises various aspects of the hardware.

"Appendix B • GNU General Public License" contains a copy of the GNU General Public License, version 2, for using and applying U-Boot, LSP, and Cavium Software Developer's Kit.

#### 1.4.2 Additional Software

For your convenience, the WANic-58xx CD-ROM also contains the following additional software:

- GNU Tool Chain includes tools for building executables for the cnMIPS cores.

- GNU Debugger is a standard debugger for the GNU software that helps diagnose a program that is executing.

"Appendix B • GNU General Public License" contains a copy of the GNU General Public License, version 2, for using and applying these tools.

# 1.4.3 Operating System Support

The WANic-58xx supports the following operating systems:

- Linux Kernel Operating System, Version  $2.6.x^1$ , which is included in the software distribution to support both the Multi-Core Processor and the host

- OCTEON Simple Executive or Generic Operating System, which the user must obtain from Cavium Networks. (*www.caviumnetworks.com*.)

## 1.4.4 Cavium Networks Users' Organization Web Site

The Cavium Networks Users' Organization web site, <u>www.cnusers.org</u>, provides a platform for expanding and supporting the user community for the OCTEON Multi-Core Processor (MIPS64) family. This web site provide a means for sharing software such as Linux-based software on the OCTEON Multi-Core Processor. This site includes data plane functions, RGMII drivers, and Simple Executive applications.

Building any applications that may use Octeon functions require the Cavium Simple Executive (CVMX) libraries, which are provided in the Cavium SDK.

Refer to the <u>www.cnuser.org</u> web site for more information on implementing specific applications.

# 1.5 Specification

Table 1-2 lists the hardware specifications for WANic-58xx models.

Table 1-2 WANic-58xx Hardware Specification

| Bereitster                                                                          | WANic Model                                                                                                                                                                  |                       |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| Description —                                                                       | 5862N-2RT                                                                                                                                                                    | 5864N-2R              |  |

| Form Factor                                                                         | PCI R3.0 dual-slot, short card                                                                                                                                               |                       |  |

| Bus Type                                                                            | PCI-X/PCI interface (33 or 66 MHz / 66 or 133 MHz)                                                                                                                           |                       |  |

| Processor                                                                           | CN586                                                                                                                                                                        | 60 NSP @ 600 MHz      |  |

| cnMIPS64 cores                                                                      | 16                                                                                                                                                                           | 16                    |  |

| Flash                                                                               |                                                                                                                                                                              | 128 MB                |  |

| DDR2 SDRAM                                                                          | 2 GB                                                                                                                                                                         | 2 GB                  |  |

| Optional RLDRAM                                                                     |                                                                                                                                                                              | 256 MB                |  |

| EEPROM                                                                              |                                                                                                                                                                              | 64 KB                 |  |

| SFPs                                                                                | Copper                                                                                                                                                                       | Fiber                 |  |

| Cooling Device                                                                      | Pas                                                                                                                                                                          | ssive Heat Sink       |  |

| Power Requirements                                                                  |                                                                                                                                                                              |                       |  |

| Maximum                                                                             | L                                                                                                                                                                            | ess than 42W          |  |

| Compliance                                                                          |                                                                                                                                                                              |                       |  |

| CE Mark                                                                             |                                                                                                                                                                              | Yes                   |  |

| Emissions Class A<br>(See also the section entitled "Emission<br>Compliance Notice" | Australia – AS/NZS CISPR 22 Class A ITE<br>Canada – ICES-003 Issue 4 Class A<br>Europe – EN55022 Class A ITE<br>Japan – VCCI Class A ITE<br>USA – FCC 47 CFR Part 15 Class A |                       |  |

| Immunity                                                                            | Euro                                                                                                                                                                         | pe – EN55024:ITE      |  |

| Safety                                                                              | Canada – CSA22.2 NO 60950-1<br>Europe – EN60950-1<br>USA – UL60950-1                                                                                                         |                       |  |

| Flammability                                                                        | UL94V0                                                                                                                                                                       |                       |  |

| Environmental Requirements                                                          |                                                                                                                                                                              |                       |  |

| NEBS                                                                                | Designed for compliance to NEBS requirements, based upon design practices as well as internal and external testing.                                                          |                       |  |

| Operating Temperature                                                               | +0° to +5.                                                                                                                                                                   | 5°C (+32° to +131°F)  |  |

| Storage Temperature                                                                 | -40° to +8                                                                                                                                                                   | 85°C (-40° to +185°F) |  |

| Relative Humidity                                                                   | 5% to 90% (non-condensing)                                                                                                                                                   |                       |  |

| Operating Altitude                                                                  | 3.9624 Kilometers (13,000 feet) maximum                                                                                                                                      |                       |  |

| Mean Time Between Failure (MTBF)                                                    |                                                                                                                                                                              |                       |  |

| Passive Heat Sink Only/ without Fan                                                 | Fan 852,639 hours                                                                                                                                                            |                       |  |

| Warranty                                                                            |                                                                                                                                                                              |                       |  |

| Module Two years                                                                    |                                                                                                                                                                              | Two years             |  |

# 1.6 Emission Compliance Notice

This equipment complies with the following international and North American emission requirements:

- Australia and New Zealand AS/NZS 3548/CISPR 22 Class A ITE

- Canada ICES-003

This Class A digital apparatus complies with Canadian ICES-003. (Cet appareil numerique de la class A est conforme a la norme NMB-003 du Canade.)

Europe — EN5022

#### WARNING

This is a Class A product. In a domestic environment, these boards may cause radio interference in which case the user may be required to take adequate measures.

#### Japan — VCCI Class A ITE

This is a Class A product based on the standard of the Voluntary Control Council for Interference from Information Technology Equipment (VCCI). If this is used near a radio or television receiver in a domestic environment, it may cause radio interference. Install and use the equipment according to the instruction manual.

USA — FCC Part 15

#### **NOTES**

The hardware has been tested and found to comply with the limits for a Class A digital device pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction in this documentation, may cause harmful interference to radio communications. Operation of the equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense. Changes or modification not expressly approved by the manufacture could void the user's FCC granted authority to operate the equipment.

# 1.7 RoHS and WEEE Compliance

GE Intelligent Platforms product initiative encourages the design of electronic products with European Union Directive 2002/95/EC – Reduction of Hazardous Substances (RoHS) environmentally-safe recycling and recovery in mind, as well as the Waste Electrical and Electronic Equipment (WEEE) reduction in the amount of hazardous chemicals used in electronic manufactures. For information on the GE Intelligent Platforms RoHS and WEEE implementation, please refer to the <a href="www.ge-ip.com">www.ge-ip.com</a> website.

# 1.8 Warranty and Repair

GE Intelligent Platforms, Inc. provides a comprehensive site on the World Wide Web (<a href="http://www.ge-ip.com">http://www.ge-ip.com</a>.) This web site contains up-to-date information including current and new products, such as the Telum family of AMC modules or ATCA Carrier Blades. The web site also contains sales office locations, copyrights, trademarks, press releases, warranties, and technical support information.

#### 1.8.1 Warranty

Warranty information is described on the GE Intelligent Platforms' web site at <a href="http://www.ge-ip.com/support/embeddedsupport/warranty">http://www.ge-ip.com/support/embeddedsupport/warranty</a>. This site provides current product warranty and repair services as well as information on specific product warranty.

#### 1.8.2 Customer Technical Support

GE Intelligent Platforms' dedicated team of Customer Technical Support Engineers is committed to providing quality support to all their customers. Customer Technical Support Engineers are trained to assist GE Intelligent Platforms' customers in the development, integration, and use of GE Intelligent Platfroms' products in customer applications, systems, and products to facilitate timely product development. The Customer Technical Support Service Center is staffed weekdays (except holidays) between the hours of 8:00 AM and 5:00 PM Central Time (CT).

Use one of the following methods to contact technical support:

Email: support.embeddedsystems.ip@ge.com

Address: GE Intelligent Platforms, Inc.

12090 South Memorial Parkway Huntsville, AL. 35803-3308

Telephone: 1-800-433-2682 Hours: 8:00 AM to 5:00 PM

Before contacting technical support, make sure you have the following information available:

- Model number

- Serial number

- Purchase receipt

- Description of problem

- System BIOS

- Driver Version

# 1.9 Handling Precautions

Read the following ESD and laser/optical precautions before handling any GE Intelligent Platforms component.

GE Intelligent Platforms, Inc. assumes no liability for the user's failure to comply with these required precautions.

#### 1.9.1 ESD Precautions

Always take the necessary precautions to prevent ElectroStatic Discharge (ESD). ESD can damage the WANic-58xx, which has ESD sensitive components.

All products should be in an anti-static plastic bag or conductive foam for storage or shipment. Work at an approved anti-static workstation when unpacking the WANic-58xx. Also, **always** use anti-static grounding straps to prevent damage due to ESD.

Use the following precautions to prevent ESD when removing the card from the antistatic packaging.

#### **CAUTION**

Always ground yourself *before* touching the board. You can ground yourself by either touching a grounded unpainted metal surface for at least two seconds, or by using an ESD-protective wrist strap from your wrist to a bare, unpainted metal section of the grounded chassis or rack. This prevents electrostatic discharge from damaging the board.

When working with a chassis, if the chassis cannot be placed upon a grounded antistatic mat, connect a grounding strap between the electrical input ground and the facility electrical service ground.

Always keep the board in its static-protective packaging when it is not installed in the system.

Always hold the board by its handles or edges. Avoid touching the components or connections on the board.

#### WARNING .

Depending on the chassis, open equipment enclosures and chassis can expose hazardous voltage which may cause electric shock to the installer. Make sure line power to the equipment is disconnected before servicing the chassis and components.

# 1.9.2 Optical/Laser Safety Notices

• For optical/laser SFP/SFP+ devices, observe the following warnings, cautions, and notes:

#### WARNING

For this product, use only the Class 1 laser device that have the following approval:

- FDA21 CFR 1040.10

- IEC 60825-1

Invisible laser radiation may be emitted from disconnected fibres or connectors. Do not Stare into beams or view directly with optical instruments as this may permanently damage your eyes.

It is important to disconnect or remove all cables before removing or installing an optical SFP transceiver. Failure to do so may result in damage to the cable or SFP device.

Protect optical SFP modules by inserting clean dust plugs into the SFP modules after the cables are extracted from them. Be sure to clean the optic surfaces of the fiber cables before plugging the dust plugs back into the optical bores of another SFP module. Avoid getting dust and other contaminants into the optical bores of your SFP modules: The optics will not work correctly when obstructed with dust.

# 2 • Hardware Description

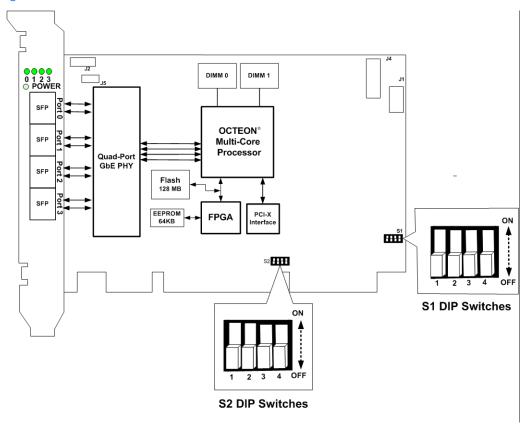

This chapter describes the hardware components on the WANic-58xx. This chapter contains a simple block diagram of the components, which include the Multi-Core Processor, memory, controllers, and external interfaces as well as connectors.

# 2.1 Hardware Components

The WANic-58xx features the following hardware components as shown in Figure 2-1:

- Cavium OCTEON Multi-Core IP Packet Processor with up to 16 cnMIPS64 cores running at rates up to 600 MHz

- PCI-X Interface, 64-bit, 133 MHz

- Field Programmable Gate Array (FPGA) for access to on-board components

- DDR2 SDRAM with 128-bit bus width plus ECC implemented in registered mini-Dual In-line Memory Modules (mini-RDIMMs)

- Up to 256 MB of optional RLDRAM II in supported configurations

- Flash Read Only Memory (ROM)

- Four front panel Ethernet I/O ports

- SFP copper or fiber-optic transceivers for front panel I/O configuration

- On-card headers provide access to the following:

- OCTEON Joint Test Action Group (JTAG) debug port

- OCTEON Enhanced JTAG debug port

- RS-232 console I/O port

- LP4 power connector

- Dual In-line Package (DIP) switches:

- S1 for board configuration

- S2 for PCI/PCI-X bus type and speed selection

- Front panel link status and activity LEDs for SFPs

Figure 2-1Block Diagram

# 2.2 Multi-Core Processor

All models of the WANic-58xx use the Cavium OCTEON family of multi-core packet processors. The OCTEON Multi-Core Processor (hereafter referred to as the Multi-Core Processor) is a single-chip packet processor for Open Systems Interconnection (OSI) Layer 2 to Layer 7 networking applications. The Multi-Core Processor provides enhanced performance, reduced power consumption, and efficient simultaneous processing of multiple tasks.

Each Multi-Core Processor option is configured at assembly time to provide comprehensive integrated functions. User choices include the following factory configured selections:

- Number of embedded cnMIPS cores

- Core clock frequencies

On select models, the Multi-Core Processor is available with up to 16 cnMIPS cores with enhancements and additional built-in hardware acceleration for content and security processing. This scalable architecture combines the cnMIPS cores with dedicated programmable coprocessor blocks to deliver up to 4 Gbps of application performance at conservative 600 MHz chip clock rates on select models.

The Multi-Core Processors offer highly-flexible external networking interfaces with four integrated Reduced Gigabit Media Independent Interface (RGMII) Ethernet ports. This provides connectivity to GbE for data plane I/O.

The Multi-Core Processor interfaces with a PCI-X host interface that can be used as a control and data interface. The PCI-X interface supports 66 MHz or 133 MHz for the PCI-X, and 33 MHz or 66 MHz for the PCI interface.

The Multi-Core Processor is powered by a dedicated on-board power supply. This permits adjustments to the core supply voltage, as needed, without affecting other circuitry.

#### 2.2.1 Multi-Core Processor Interfaces

The Multi-Core Processor contains the following interfaces:

- RGMII 1

- Two-Wire Serial Interface (TWSI)

- General Purpose I/O (GPIO)

#### **RGMII Interface 1**

The Multi-Core Processor RGMII Interface 1 functional block provides data transfer to and from the GbE PHY device using the four Reduced Gigabit Media Independent Interface (RGMII) interface ports. The GbE PHY performs serialization and de-serialization (SerDes) data transfers to and from each SFP on the WANic-58xx front panel.

RGMII Interface 0 is not implemented in this version of the WANic-58xx.

#### **TWSI Interface**

The Multi-Core Processor uses a Two-Wire Serial Interface (TWSI), which is similar to an I2C interface. For the TWSI, the Multi-Core Processor supports normal and fast modes as well as 7-bit and 10-bit interfaces. The Multi-Core Processor can operate as a master TWSI device. Any of the cores or a remote PCI host can communicate with the TWSI device. The Multi-Core Processor uses the TWSI to determine the mini-RDIMM module type. Software primitives provide access to the industry standard TWSI on the WANic-58xx. (See "Chapter 4: Software Features" for a description of these software primitives.)

#### **GPIO** Interface

The Multi-Core Processor provides a General Purpose I/O (GPIO) interface that provides an input port to detect the following signals for each SFP as shown in Figure 2-2:

- SFP presence (SFP\_PRES)

- Transmit fault (TX\_FAULT)

- SFP Loss of signal (SFP\_LOS)

Figure 2-2 GPIO Interface to SFPs

The on-card signals in Table 2-1 are allocated to the Multi-Core Processor GPIO pins.

Table 2-1 GPIO Signal Description

| GPIO PINs | Signal     | Description             |

|-----------|------------|-------------------------|

| 0–3       | SFP_PRES   | SFP presence detect     |

| 4–7       | TX_FAULT   | Transmit fault detected |

| 8–11      | SFP_LOS    | SFP loss of signal      |

| 12        | RGMII _INT | RGMII interrupt         |

| 13        | RSVD       | Reserved                |

| 14        | FPGA_INT   | FPGA interrupt          |

| 15        | RSVD       | Reserved                |

#### 2.2.2 Multi-Core Processor Boot Bus

The Multi-Core Processor Boot Bus (hereafter referred to as the Boot Bus) provides an 8-bit data path with:

- 28 address lines (using big endian byte-ordering)

- Eight Chip Selects (control pins) that provide access to devices connected to the Boot Bus

- Independent read and write

The Boot Bus connects directly to the Flash, which is controlled by Chip Select 0. FPGA registers are also accessible through the Boot Bus by using Chips Select 1.

When power-on reset occurs, Core 0 of the Multi-Core Processor uses the Boot Bus to obtain code for the core that controls Chip Select 0 unless the WANic-58xx is configured to boot from the PCI-X (using the S1 DIP Switch).

# 2.3 PCI/PCI-X Interface

The WANic-58xx is a target (add-in) card on the PCI/PCI-X Interface. The Multi-Core Processor interfaces directly to the PCI/PCI-X interface and receives the PCI/PCI-X clock from the host. The S2 DIP Switch provides the means to configure the capabilities of the PCI/PCI-X Bus for the WANic-58xx, which the host determines at reset. The following capabilities can be selected:

- For PCI-X 66 MHz or 133 MHz

- For PCI −33 MHz or 66 MHz

A PCI/PCI-X Bus Controller uses the power-on reset state of the PCI bus to generate the input clock for all devices on the bus.

- For PCI-X —The bus controller drives the associated initialization pattern to all

devices on the bus to configure them according to the sampled state of the bus

signals at reset. The Multi-Core Processor configures the internal PCI-X bus logic

automatically based on the initialization pattern initiated by the PCI/PCI-X Bus

Controller.

- For PCI Logic is configured according to the timing of the input clock signal.

See "Section 2.8" Dual In-Line Package (DIP) Switches" for more information on configuring the PCI/PCI-X Bus.

#### 2.4 FPGA

The FPGA on the WANic-58xx provides a software interface to various on-board hardware resources. The FPGA contains registers that allow the Multi-Core Processor and PCI/PCI-X host to control and to monitor transactions among interfaces and local hardware resources.

The FPGA routes individual reset signals to the Flash memory, mini-RDIMM memory, and GbE transceiver devices. These resets are asserted at power-up, and are de-asserted automatically once power is stable. Software can also force an individual reset to these devices using the **Peripheral Reset Register**. (See "Chapter 3.1: FPGA General Registers" for more information on this and other FPGA registers.)

A PCI\_RESET from the host does not directly reset these devices.

The FPGA registers interface to the Multi-Core Processor by means of the Boot Bus and Chip Select logic. The Multi-Core Processor must be configured to assert this Chip Select to enable access to FPGA registers in the desired range of the address space according to software needs.

All FPGA registers are mapped to a contiguous block of 32 bytes within the address space. In cases when the Chip Select logic configuration accesses a range of addresses larger than 32 bytes, the FPGA register image repeats.

#### **I2C Interface**

The FPGA also provides independent I2C ports to six interfaces with the following devices:

- Four front panel SFPs

- A 64 KB serial EEPROM

- A temperature sensor

The FPGA performs read and write operations on each I2C interface in response to requests from the Multi-Core Processor through specific FPGA registers. See "Chapter 3.2: I2C Registers" for a description of each FPGA register.

# 2.5 Memory

The main memory on the WANic-58xx consists of DDR2 SDRAM and, optionally, RLDRAM memory. Flash memory provides storage for initial boot code.

#### **2.5.1 DDR2 SDRAM**

The WANic-58xx supports up to 2 GB<sup>1</sup> of DDR2 SDRAM memory operating at speeds up to 667 MHz and a full 128-bit data path. An additional 16 bits provide ECC support. ECC permits 1-bit error correction, and 2- and 3-bit error detection. Timing for the DDR2 SDRAM interface is derived from an independent reference clock and is not dependent on the processor core frequency. The Multi-Core Processor directly controls the DDR2 SDRAM.

#### Mini-RDIMMs

The DDR2 SDRAM is implemented as two socketed miniature registered Dual In line Memory Modules (Mini-RDIMMs) with 512 MB or 1 GB each depending on the model. The WANic-58xx use registered mini-RDIMMs with ECC support. Each vertical Mini-RDIMM socket provides a 64-bit data bus and ECC. To ensure the clock signal integrity, Mini-RDIMMs are built with address line registers and clock Phase Lock Loop (PLL). The WANic-58xx supports both single- and dual-rank Mini-RDIMMs.

Contact Customer Technical Support for a listing of supported memory.

#### Serial Presence Detect

Each Mini-RDIMM module features a Serial Presence Detect (SPD) based on a serial EEPROM device, which uses the I2C protocol to access information about each Mini-RDIMM. Mini-DIMM sockets (0 and 1) are connected to the Multi-Core Processor, TWSI I2C interface, and hardwired to device addresses **0x50** and **0x54** respectively.

#### **Reference Clock**

Timing for the DDR2 SDRAM is derived from an independent reference clock input. The reference clock frequency is chosen to match the speed of the DDR2 SDRAM devices connected to the interface.

The DDR2 SDRAM reference clock is derived from a crystal and PLL frequency multiplier. The reference clock frequency can be programmed through hard strap selection at the factory to permit DDR2 data transfer rates of up to 667 MHz.

# 2.5.2 Optional RLDRAM II

The RLDRAM II (hereafter referred to as RLDRAM) is optional on all WANic-58xx models. Consult with your GE Intelligent Platforms sales representative for detailed information.

The RLDRAM interface supports up to 256 MB of externally connected RLDRAM over two independent 18-bit data paths. The effective data transfer rate is further enhanced by interleaving memory accesses between the two banks. The WANic-58xx supports two optional RLDRAM devices per 18-bit data path, for a total of four RLDRAMs.

The Multi-Core Processor generates the RLDRAM clocks, which run at half the core clock frequency. The data transfer rate matches the core clock frequency.

<sup>1.</sup> Additional configuration are available. Please contact GE intelligent Platforms Customer Technical Support or Sales for information.

#### 2.5.3 Flash

The WANic-58xx contains a 128 MB Flash EEPROM device (hereafter referred to as the Flash). Code execution is supported from this Flash during hardware initialization only. The Flash is connected directly to the Multi-Core Processor Boot Bus as shown in Figure 2-3.

Flash boot occurs when DIP Switch 3 is set to the Off position.

To optimize code performance, the operating firmware copies the boot code into the DDR2 SDRAM for use following hardware initialization. The Flash device has the ability to be written to, or erased, when required by operating firmware.

Figure 2-3 Flash Connection to Boot Bus

The Flash has an active low hardware reset pin (/FLASH\_RESET). This hardware reset pin terminates all operations in progress and resets the Flash, after which the Flash is ready for a new operation. The Flash reset is asserted at power-up and is automatically de-asserted once power is stable. Software forces a reset of the Flash by setting the appropriate bit in the **Peripheral Reset Register**. (See "Chapter 3: FPGA Registers" for more information on this and other FPGA registers.)

A PCI\_RESET from the host does not directly reset the Flash.

#### 2.5.4 Serial EEPROM

The serial EEPROM provides 64 KB of general-purpose non-volatile data storage for on-board specific hardware configuration information, such as assembly model number, serial number, and so forth. An I2C interface connects the EEPROM to the Multi-Core Processor by means of the FPGA. This permits examination and modification of the EEPROM contents.

# 2.6 Gigabit Ethernet PHY Devices

The WANic-58xx contain a GbE physical (PHY) device, which is a Marvell® 88E1143 quad-port PHY. This GbE PHY is a high-performance quad GbE device that provides four independent ports and interconnects serial data on the Multi-Core Processor by means of four RGMII interface ports. The GbE PHY implements the IEEE 802.3z Physical Coding Sublayer (PCS).

This GbE PHY is factory-configured to support either copper or optical SFPs in Serial Gigabit Media Independent Interface (SGMII) mode. Copper SFPs are desirable when using SGMII mode because copper provides the ability to operate the link at 10, 100, and 1000BASE-T data rates.

In SGMII mode, four 1000Base-T Ethernet ports are provided through four SFP receptacles on the front panel. These four ports implement all standard PHY interface functions defined in the IEEE 802.3-2000 specification and supports standard 802.3 Ethernet frames plus 802.1p/q VLAN functions. When the GbE PHY is in use, the Multi-Core Processor automatically determines the type of SFP and controls them directly using an I2C interface for each SFP.

The GbE PHY contains several registers to manage the device. These registers are interconnected with the Multi-Core Processor by means of a standard two-wire Management Data I/O (MDIO) interface. The Multi-Core Processor contains a dedicated System Management Interface (SMI) Controller for communicating with this interface.

The GbE PHY has four identical ports, each with associated management registers. The MDIO address is comprised of a 5-Bit PHY address field and a 5-Bit register address field. When accessing the GbE PHY management registers within the WANic-58xx, note that PHY addresses 0-3 correspond to I/O ports 0-3.

The GbE PHY reset is asserted at power-up, and de-asserted automatically once power is stable. Software can also force an individual reset to the PHY device using the **Peripheral Reset Register**.

A PCI RESET from the host does not reset this device.

# 2.7 SFP Front Panel Connectors

The WANic-58xx provides a flexible configuration of copper SFPs or single-mode or multi-mode optical SFP modules. SFP modules insert into front panel slots in the WANic-58xx to provide network connections to external line interfaces. SFP copper ports use a standard RJ-45 connector. SFP fiber ports use a standard LC connector.

The FPGA provides an I2C interface for each SFP. The I2C interface can be used to determine the type of SFP installed, and to configure each SFP accordingly.

The GbE PHY also provides an LED interface to indicate link status and activity for each SFP. See "Section 2.10.1" "LEDs" for more information.

Contact Customer Technical Support for a list of certified SFPs.

# 2.8 Dual In-Line Package (DIP) Switches

As shown in Figure 2-4, the WANic-58xx contains two sets of DIP Switches, which toggle on and off:

- S1

- S2

#### 2.8.1 S1 DIP Switch

The S1 DIP Switch has a bank of four dual-position DIP Switches, which are located towards the edge of the board and collectively labeled S1 as shown in Figure 2-4. Use the S1 DIP Switch to perform the following:

- FPGA programming

- EJTAG access

- Selects the Boot mode

- Boot the diagnostic utility

The **Board ID** and **DIP** Switch Register indicates the boot selection as either booting from the Flash or the PCI-X host. The following considerations should be noted:

- For JTAG Boundary Scan Tests, DIP Switch 1 and 2 must be in the On position.

- For JTAG testing of the FPGA only, DIP Switch 1 must be in the Off position to access the FPGA.

- When using EJTAG with a debugging probe for the Multi-Core Processor, DIP Switch 2 must be in the Off position.

- Use DIP Switch 3 to select either Flash or PCI-X boot mode.

- Turn DIP Switch 4 to the On position to start the on-board diagnostics.

Figure 2-4 DIP Switches

Table 2-2 through Table 2-3 summarize the DIP Switch settings for JTAG, Boot, and Diagnostic modes.

Table 2-2 JTAG Mode S1 DIP Switch Configuration

| Mode | Operation –                                                       | DIP SWITCH |     |

|------|-------------------------------------------------------------------|------------|-----|

|      |                                                                   | 1          | 2   |

|      | Configures the board/MPU for use with EJTAG debugger              | Off        | ON  |

|      | Configures the board for JTAG programming of the FPGA             | Off        | Off |

| JTAG | Not supported                                                     | ON         | Off |

|      | Configures the board for boundary scan testing on full JTAG chain | ON         | ON  |

Table 2-3 Boot Mode S1 DIP Switch Configuration

| Mode | Operation                     | DIP SWITCH |

|------|-------------------------------|------------|

| Mode | Operation                     | 3          |

| Boot | Enables Flash Boot operations | Off        |

| ВООТ | Enables PCI-X boot operations | ON         |

Table 2-4 Diagnostic Mode S1 DIP Switch Configuration

| Mode       | Operation                                | DIP SWITCH |

|------------|------------------------------------------|------------|

| Mode       | Operation                                | 4          |

| Diagnostic | Disables Linux auto-start                | Off        |

| Diagnostic | Enables auto-start Linux and Diagnostics | ON         |

#### 2.8.2 S2 DIP Switch

The S2 DIP Switch contains a bank of four two-position DIP Switches located towards the bottom center of the board and labeled S2 as shown in Figure 2-4. Use the S2 DIP Switches to configure the PCI/PCI-X bus type and speed.

In Table 2-5 a dash (-) indicates that the switch is not used for that bus type. The default setting for each switch is Off.

Table 2-5 S2 DIP Switch

| SW1 | SW2 | SW3 | SW4 | Bus Type        | Speed   |

|-----|-----|-----|-----|-----------------|---------|

| Off | Off | _   | _   | PCI-X (default) | 133 MHz |

| Off | ON  | _   | _   | PCI-X           | 66 MHz  |

| ON  | _   | Off | _   | PCI             | 66 MHz  |

| ON  | _   | ON  | _   | PCI             | 33 MHz  |

## 2.9 Reference Clock Circuitry

Figure 2-5 illustrates the Multi-Core Processor reference clock circuitry. The Multi-Core Processor core reference clock input is driven by a fixed 50 MHz oscillator. A PLL within the Multi-Core Processor derives the internal core clock frequency according to certain values on the Multi-Core Processor. The 50 MHz oscillator permits the core clock frequencies of 600 MHz on the WANic 58xx models to be driven from the common reference frequency.

The 50 MHz signal is also routed to the FPGA clock input.

The Multi-Core Processor receives the PCI-X/PCI clock from the host PCI-X interface.